NORTH AMERICAN ARC ALMA Regional Center North American ALMA Science Center

Development Upgrades of the Atacama Large Millimeter/submillimeter Array (ALMA)

# **Study Report**

## EXAMINE IF THE NRC ALMA VERY COARSE CHANNELIZER FPGAS CAN HANDLE 16 GHz per sideband per polarization

PRINCIPAL INVESTIGATOR AND PRIMARY AUTHOR: THUSHARA GUNARATNE

CONTRIBUTING AUTHORS: BRENT CARLSON, MIKE PLEASANCE, AND STEPHEN HARRISON

INSTITUTION: THE NATIONAL RESEARCH COUNCIL OF CANADA – HERZBERG ASTRONOMY AND ASTROPHYSICS RESEARCH CENTER

ADDRESS: PO BOX 248, PENTICTON, BC, CANADA V2A 6J9

PI CONTACT INFORMATION: 250-497-2341 Thushara.Gunaratne@nrc-cnrc.gc.ca

| Prepared By        | Name         | Thushara Gunaratne | Signatura   | $\mathcal{A}_{I}$ |            |

|--------------------|--------------|--------------------|-------------|-------------------|------------|

|                    | Organization | NRC                | - Signature | ha                | 2022-02-11 |

| <b>Reviewed By</b> | Name         | Brent Carlson      | Signaturo   |                   |            |

| _                  | Organization | NRC                | Signature   |                   |            |

|                    | Name         | Mike Pleasance     | Signatura   |                   |            |

|                    | Organization | NRC                | Signature   |                   |            |

|                    | Name         | Stephen Harrison   | Signaturo   |                   |            |

|                    | Organization | NRC                | - Signature |                   |            |

### TABLE OF CONTENTS

| TABLE OF      | FIGURES                             |                                          | 4                                      |

|---------------|-------------------------------------|------------------------------------------|----------------------------------------|

| TABLE OF      | TABLES                              |                                          | 6                                      |

| LIST OF A     | CRONYMS AND TERMS .                 |                                          | 7                                      |

| 1 Exec        | cutive Summary                      |                                          | 9                                      |

| 2 Back        | kground                             |                                          |                                        |

| 3 Stud        | ly Approach                         |                                          |                                        |

| 4 Ove         | rview                               |                                          |                                        |

| 4.1           | The Basics of Oversamp              | ed Polyphase Filter-Banks                |                                        |

| 4.1.1         | 1 Single Stage Implei               | nentation of Oversampled Polyphas        | e Filter-Banks16                       |

| 4.1.2         | 2 Two Stage Implem                  | entation of Oversampled Polyphase        | Filter-Banks18                         |

| 4.2<br>Proces | •                                   | re of the Two-Stage Oversampled F        | Polyphase Filter-Bank for Sub-Band<br> |

| 4.3           |                                     | e Two-Stage Oversampled Polyphas         |                                        |

|               | -                                   |                                          |                                        |

| -             |                                     |                                          |                                        |

|               | •                                   |                                          |                                        |

| 6.1           |                                     |                                          |                                        |

| 6.2           |                                     |                                          |                                        |

| 6.3           |                                     |                                          |                                        |

| 6.3.1         |                                     | •                                        |                                        |

| 6.3.2         |                                     |                                          |                                        |

| 6.3.3         |                                     |                                          |                                        |

| 6.3.4         |                                     |                                          |                                        |

| 6.3.5         |                                     |                                          |                                        |

| 6.3.6         |                                     |                                          |                                        |

| 6.3.7         |                                     |                                          |                                        |

| 6.3.8         |                                     |                                          |                                        |

|               |                                     |                                          |                                        |

| 7.1           |                                     | -                                        |                                        |

| 7.1.1         |                                     |                                          |                                        |

| 7.1.2         |                                     | -                                        |                                        |

| 7.1.3         |                                     |                                          |                                        |

| 7.2           | Synthesis of 20 Instance            | s of OSPFBs and other Key Firmware       | e Blocks                               |

|               | National Research<br>Council Canada | Conseil national<br>de recherches Canada | Canada                                 |

Council Canada de recherches Canada

| Cycle 9 NA ALMA Development Study Report – Examine if the NRC ALMA Very Coarse Channelizer | FPGAs |

|--------------------------------------------------------------------------------------------|-------|

| Can Handle 16 GHz per sideband per polarization (SUBMIT - 2022-02-11)                      | 3     |

|    | 7.2.1   | Resource Utilization Summary                                                              | 48 |

|----|---------|-------------------------------------------------------------------------------------------|----|

|    | 7.2.2   | Routing Congestion                                                                        | 50 |

|    | 7.2.3   | Static Timing Analysis and F <sub>max</sub> Estimates                                     | 51 |

| 8  | Risks . |                                                                                           | 51 |

| 9  | Conclu  | usions                                                                                    | 52 |

| 10 | Refere  | ences                                                                                     | 52 |

| 11 | Apper   | ndix—Preference between Sub-Bands of 1.6 GHz and 2.0 GHz of Bandwidth                     | 54 |

| 1  | .1.1 C  | Over-Sampled Polyphase Filter Bank Resources                                              | 54 |

| 1  | .1.2 L  | ogic and Mapping for AVCC Data Ingest                                                     | 55 |

| 1  | .1.3 C  | Distribution of 200 MHz AVCC Frequency Slices                                             | 55 |

| 12 | Apper   | ndix—F <sub>max</sub> Estimates for the Internally Generated Clocks in 100G Ethernet MACs | 57 |

#### TABLE OF FIGURES

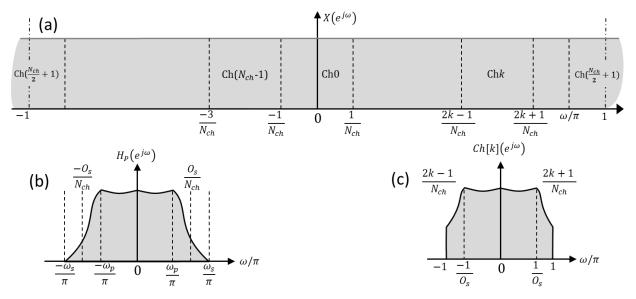

| Figure 4-1      | Segmentation of the input spectrum by a $N_{Ch}$ -channel over-sampling channelizer having      |

|-----------------|-------------------------------------------------------------------------------------------------|

| the over-samp   | ling factor $O_s$ (a), the magnitude transfer function of the prototype filter $HP(z)$ (b), and |

| the output ma   | gnitude spectrum of $ch[k](n)$ (c)                                                              |

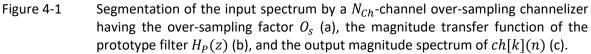

| Figure 4-2      | Single stage OSPFB architecture                                                                 |

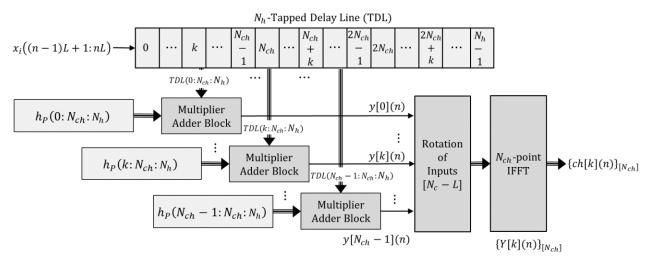

| Figure 4-3      | System view of a two stage OSPFB                                                                |

| Figure 4-4      | Typical magnitude responses of the prototype filter of the OSPFB for stage-1 (a) and the        |

| Half-Band filte | r (b) for the above two-stage implementation of the functionality of OSPFB                      |

| Figure 4-5      | An efficient implementation of a Half-Band filter                                               |

| Figure 4-6      | Proposed architecture of the OSPFB for extracting FSs from the sub-bands20                      |

| Figure 4-7      | Magnitude response of the prototype filter for the stage-1 OSPFB22                              |

| Figure 4-8      | Magnitude response of the Half-Band filter of order 46                                          |

| Figure 4-9      | Combined magnitude response of the prototype filter of the stage-1 OSPFB and the Half-          |

| Band filter.    |                                                                                                 |

| Figure 4-10     | Magnitude (top) and phase (bottom) spectra of the input test vector to the OSPFB24              |

| Figure 4-11     | Top-Row : Magnitude (left) in dB-scale and phase (right) spectra of the output channels         |

| (blue) after ga | in correction and the corresponding segmented spectra of the input test vector (red) to         |

| the OSPFB. Bo   | ttom-row: Differences between segmented input and output magnitude (left) in dB-scale           |

| and phase (rig  | ht) spectra24                                                                                   |

| Figure 4-12     | Impulse responses of the OSPFB: real-part (top) and imaginary-part (bottom). The                |

| impulse respo   | nse spans a maximum of 27 output samples25                                                      |

| Figure 6-1      | Input/output interfaces for the ALMA OSPFB segmenting the sub-bands and generating              |

| FSs.            |                                                                                                 |

| Figure 6-2      | Arrangement of the real and complex components of the input samples of the sub-band             |

|                 | array 't_CPLX_STRM_a(0:4)'                                                                      |

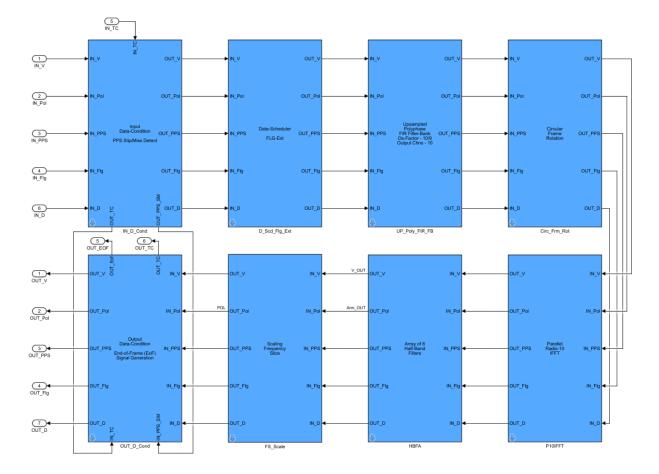

| Figure 6-3      | Modularized architecture of the two-stage OSPFB_IP firmware-block                               |

| Figure 6-4      | Re-arranged input data frame in Input Data-Condition PPS Slip/Miss Detect module31              |

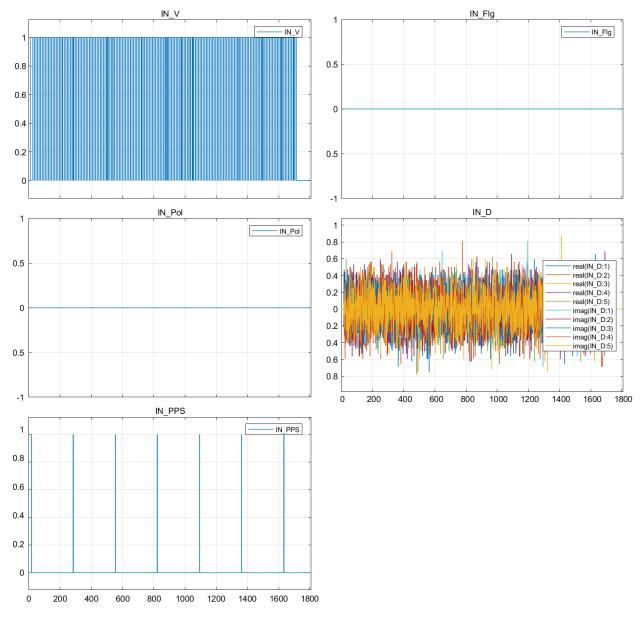

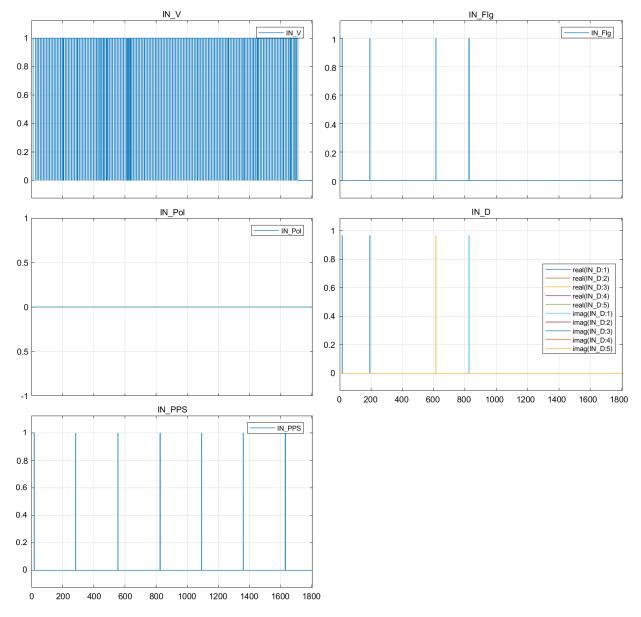

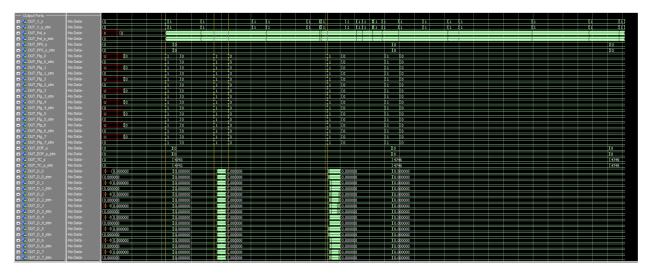

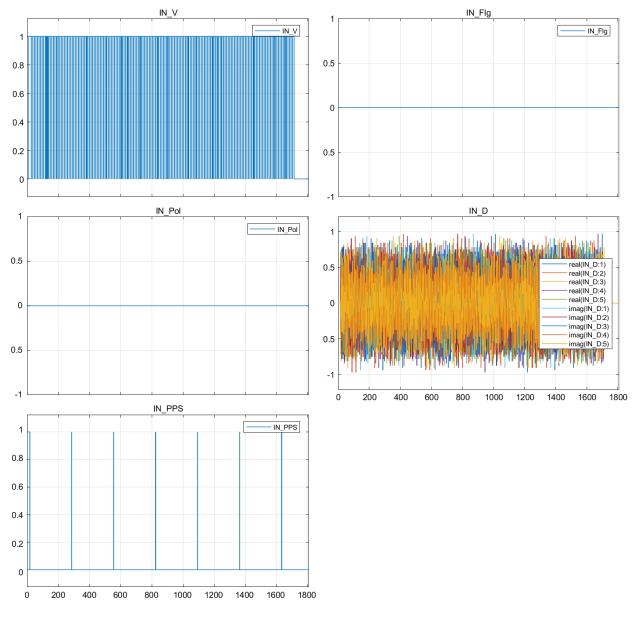

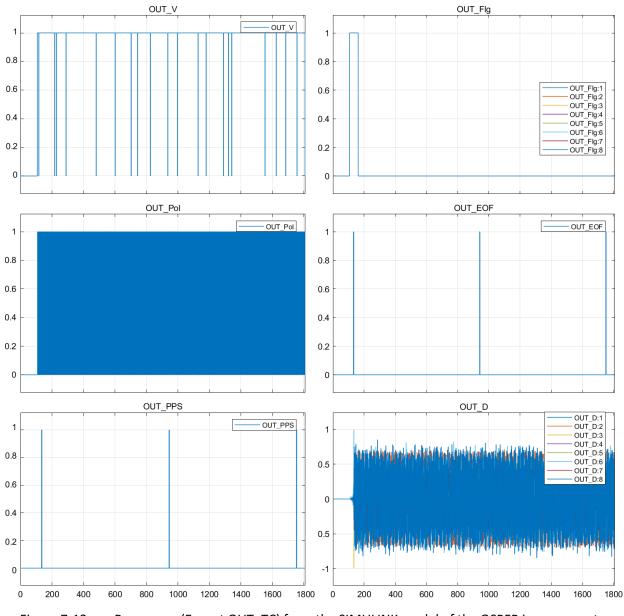

| Figure 7-1      | Stimuli (Except IN_TC) containing Gaussian distributed test vectors fed to the SIMULINK         |

|                 | OSPFB                                                                                           |

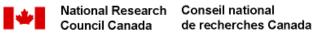

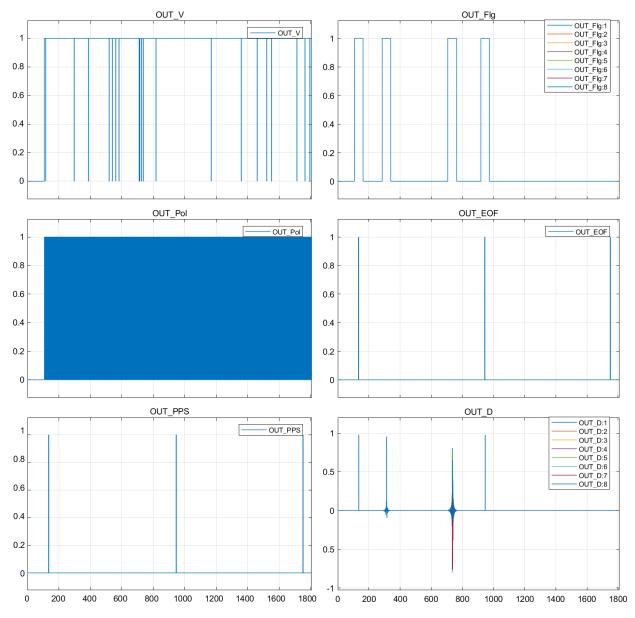

| Figure 7-2      | Responses (Except OUT_TC) from the SIMULINK model of the OSPFB in response to                   |

|                 | in Figure 7-1                                                                                   |

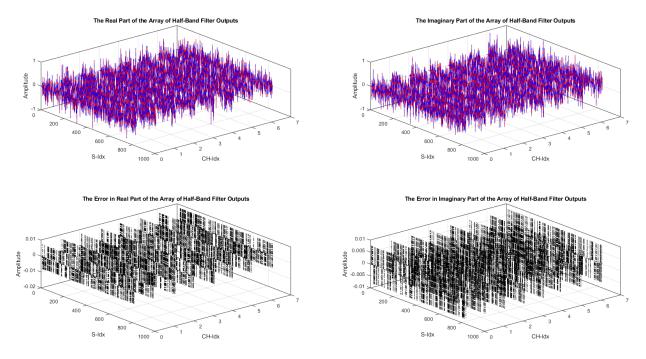

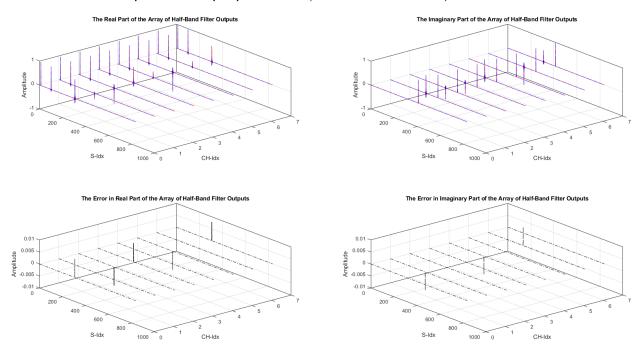

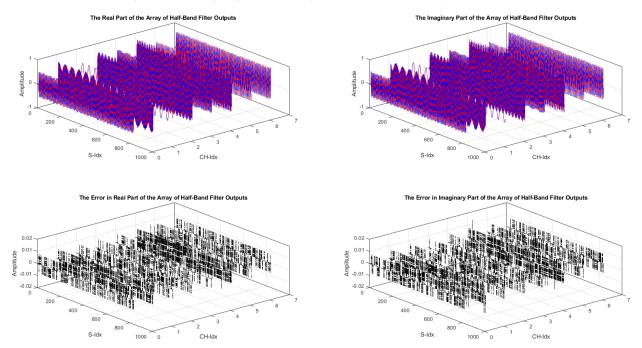

| Figure 7-3      | Comparison between re-quantized FS outputs from MATLAB implementation and                       |

| -               | lementation of the two-stage OSPFB for Gaussian distributed inputs                              |

| Figure 7-4      | Stimuli for the ModelSim simulation – with Gaussian-distributed inputs                          |

| Figure 7-5      | Comparison of responses from ModelSim simulation and the SIMULINK model for                     |

|                 | ibuted inputs                                                                                   |

| Figure 7-6      | Stimuli (Except IN_TC) containing impulses fed to the SIMULINK model of the OSPFB39             |

| Figure 7-7      | Responses (Except OUT_TC) from the SIMULINK model of the OSPFB in response to                   |

|                 | in Figure 7-6                                                                                   |

| Figure 7-8      | Comparison between re-quantized FS outputs from MATLAB implementation and                       |

|                 | lementation of the two-stage OSPFB for impulsive inputs                                         |

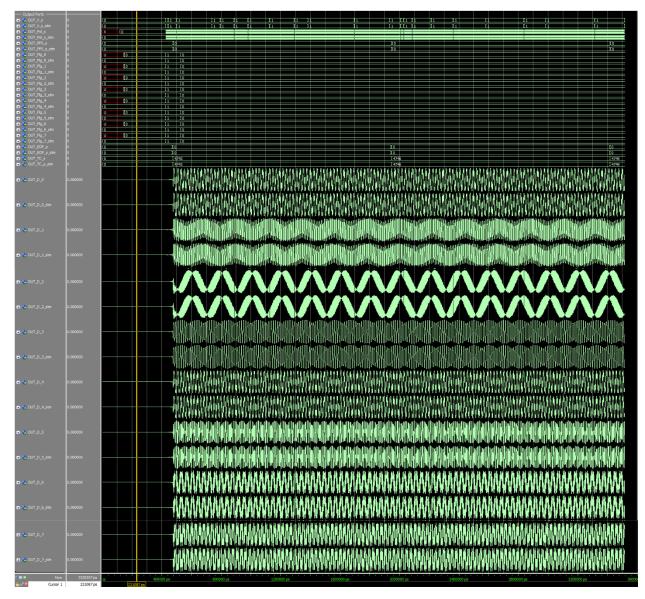

| Figure 7-9      | Stimuli for ModelSim simulation – with impulsive inputs                                         |

| Figure 7-10     | Comparison of responses from ModelSim simulation and the SIMULINK model - for                   |

| impulsive inpu  | its41                                                                                           |

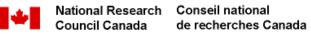

National Research Conseil national Council Canada de recherches Canada

| Figure 7-11<br>OSPFB. | Stimuli (Except IN_TC) containing sum of 8 sinusoids fed to the SIMULINK model of the    |

|-----------------------|------------------------------------------------------------------------------------------|

| Figure 7-12           | Responses (Except OUT_TC) from the SIMULINK model of the OSPFB in response to            |

| stimuli shown         | in Figure 7-11                                                                           |

| Figure 7-13           | Comparison between re-quantized MATLAB implementation and SIMULINK                       |

| implementatio         | on of the two-stage OSPFB for sum of sinusoids inputs45                                  |

| Figure 7-14           | Stimuli for ModelSim simulation - with sum of sinusoids45                                |

| Figure 7-15           | Comparison of responses from ModelSim simulation and the SIMULINK model – for sum        |

| of sinusoids.         |                                                                                          |

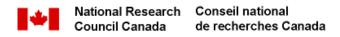

| Figure 7-16           | Strawman architecture for the AVCC FPGA                                                  |

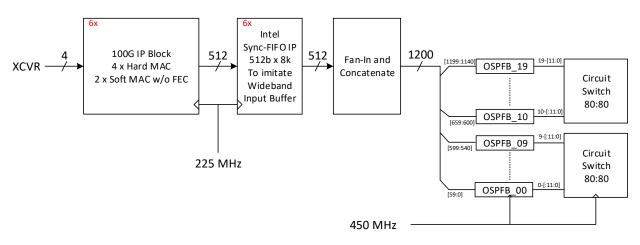

| Figure 7-17           | Multiple views showing placement of logic resources on the chip for the key firmware     |

| blocks. (A) the       | six 100G Ethernet MACs; (B) the six Sync- FIFOs (C) 20 OSPFB firmware blocks and (D) two |

| 80x80 Circuit S       | Switch firmware blocks                                                                   |

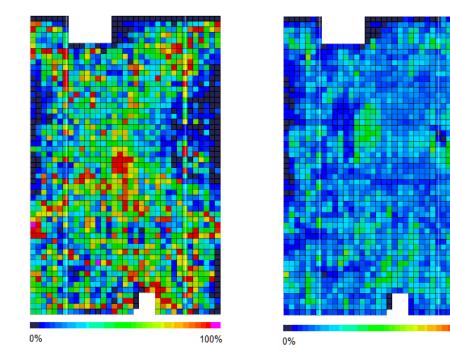

| Figure 7-18           | Utilization of 'long' (left) and 'short' (right) wires for routing in the AVCC FPGA      |

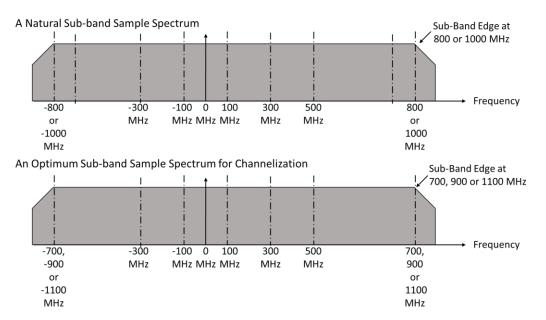

| Figure 11-1           | The natural distribution of bandwidth for sub-bands sampled at 2.0 Gs/s and 2.5 Gs/s     |

| containing 1.6        | GHz and 2.0 GHz of bandwidth, respectively (top) and the optimum bandwidth               |

| distribution fo       | r segmentation into FSs containing 200 MHz of bandwidth (bottom)                         |

#### TABLE OF TABLES

| Table 4-1                 | The key parameters associated with the OSPFBs22                                                | L |

|---------------------------|------------------------------------------------------------------------------------------------|---|

| Table 6-1                 | Components of the VHDL record 't_CPLX_STRM'                                                    | 7 |

| Table 6-2                 | List of monitor and control registers for the ALMA OSPFB firmware block                        | ) |

| Table 6-3                 | The mapping of the 't_CPLX_STRM_a(0:4)' to the inputs of the Input Data-Condition PPS          |   |

| Slip/Miss De              | etect module                                                                                   | ) |

| Table 6-4                 | The mapping of the outputs of the Output Data-Condition module and the eight records           |   |

| 't_CPLX_STR               | RM_a(0:7)' correspond to the FSs                                                               | 3 |

| Table 7-1                 | Properties of the 8 sinusoids used in combination as the input stimulus42                      | 2 |

| Table 7-2                 | Resource usage summary from the Fitter of the Intel Quartus compilation flow48                 | 3 |

| Table 7-3                 | The main clocks needed for AVCC FPGA, required clock rates, $F_{max}$ estimates and worst-case |   |

| operating co              | ondition52                                                                                     | L |

| Table 11-1                | The design configurations and estimates of required multiplier for the two-stage OSPFBs        |   |

| to extract FS             | Ss from sub-bands sampled at 2.0 Gs/s and 2.5 Gs/s54                                           | 1 |

| Table 12-1                | The derived clocks needed for the 100G Ethernet MACs in the AVCC FPGA, required clock          |   |

| rates, F <sub>max</sub> e | stimates and worst-case operating condition5                                                   | 7 |

| ALMA Frequency Slice Processor<br>Atacama Large Millimeter/submillimeter Array       |

|--------------------------------------------------------------------------------------|

|                                                                                      |

|                                                                                      |

| ALMA TALON Correlator Beamformer                                                     |

| ALMA TALON Correlator Data Processor                                                 |

| ALMA TALON Central Signal Processor                                                  |

| ALMA TALON Hardware In the Loop Simulator                                            |

| ALMA Very Coarse Channelizer                                                         |

| Device Tree Interconnect. A custom interface to interconnect firmware blocks.        |

| Double Side Band                                                                     |

| Forward Error Correction                                                             |

| Correlator architecture where two cascading frequency segmentation stages followed   |

| by the cross-correlator.                                                             |

| Correlator architecture where the initial frequency segmentation is performed at the |

| antenna followed by two cascading frequency segmentation stages followed by the      |

| cross-correlator.                                                                    |

| First-In-First-Out (memory) buffer                                                   |

| Finite Impulse Response                                                              |

| Field Programmable Gate Array                                                        |

| Frequency-Slice                                                                      |

| Finite State Machine                                                                 |

| Giga (i.e. 10 <sup>9</sup> ) samples per second                                      |

| Herzberg Astronomy and Astrophysics (Research Center under the NRC, CANADA)          |

| Hardware Description Language                                                        |

| Inverse Discrete Fourier Transform                                                   |

| Inverse Fast Fourier Transform                                                       |

| Laboratoire d'astrophysique de Bordeaux (Université of Bordeaux, FRANCE)             |

| Lower Side Band                                                                      |

| Media Access Controller (in Transceivers )                                           |

| Mega (i.e. 10 <sup>6</sup> ) samples per second                                      |

| North America                                                                        |

| National Radio Astronomy Observatory (USA)                                           |

| National Research Council (CANADA)                                                   |

| National Science Foundation (USA)                                                    |

| Oversampled Polyphase Filter-Bank                                                    |

| Parallel Inverse Fast Fourier Transform                                              |

| Register Transfer Level                                                              |

| Square Kilometre Array (www.skatelescope.org)                                        |

| Serial Lightweight Interconnect Mesh                                                 |

| Static Timing Analysis                                                               |

| Talon Demonstrator Correlator                                                        |

| Tapped Delay Line                                                                    |

| Upper Side Band                                                                      |

| VLSI (Very Large Scale Integration) Hardware Description Language                    |

| Wideband Input Buffer                                                                |

|                                                                                      |

### LIST OF ACRONYMS AND TERMS

### **ACKNOWLEDGEMENTS**

We would like to thank Crystal Brogan for her support in clarifying interface matters between the Digitizer and the Correlator and her comments on the first version of this report.

## **1** Executive Summary

The 2018 ALMA Development Roadmap [3] identified at least doubling ("2x") the correlated bandwidth of ALMA from 8 GHz to 16 GHz per polarization as its number one near-term priority. This major development initiative has come to be known as the ALMA 2030 Wideband Sensitivity Upgrade (WSU). As originally submitted to the North American ALMA Development Project Call, the NRC's "2<sup>nd</sup> *Generation ALMA Correlator/Beamformer – the ALMA TALON Central Signal Processor"* (AT.CSP) would only be able to ingest, coarsely channelize into 200 MHz increments called Frequency-Slices (FSs), and correlate 2x BW (i.e., 16 GHz per pol) within the proposal cost-cap, though it would be expandable to larger bandwidth when more funding becomes available in the future. However, recent advancements in digitizer technology have demonstrated the potential of *quadrupling* ("4x") the digitized bandwidth to 32 GHz per polarization [8], i.e., 16 GHz per sideband per pol. Subsequently, the ALMA Project has expressed strong interest in eventually achieving 4x Correlated BW.

Based on design advances that occurred after the initial AT.CSP Project proposal submission [1], this 3month-long NA Development Study was initiated to investigate if a single ALMA Very Coarse Channelizer (AVCC), each with 2 FPGAs, can be used to ingest and coarsely channelize the full 16 GHz per sideband per pol digitized data stream with the already costed resources. In this scenario, future bandwidth expansion will only require additional hardware for the fine channelization and correlation stage, and in the meantime a user will be able to flexibly select exactly which 16 GHz per pol (from the 32 GHz per pol of digitized data) is sent on for fine channelization and correlation in FSs. Additionally, the resulting detailed design work for the AVCC stage presented here represents a significant jump-start towards one of the initial project milestones of finalizing detailed FPGA designs.

After considerable cross-subsystem discussion and refinement, it has been agreed that a first subbanding will occur in the antennas in the Back-end subsystem. In the agreed design, the 32 GHz of science bandwidth per polarization contained in the 40 Gs/s sampled sequence will be segmented into sub-bands within the Digitizer subsystem. These sub-bands will be then transferred to the AT.CBF and further segmented into FSs in the AVCCs. One key topic has not yet been resolved, namely the exact nature of the first-F sub-banding, though the NRC and LAB teams agreed to consider two options:

Option 1: Sampled at 2.0 Gs/s containing 1.6 GHz (3.2 GHz for DSB) of bandwidth and

Option 2: Sampled at 2.5 Gs/s containing 2.0 GHz (4.0 GHz for DSB) of bandwidth,

both consisting of complex-valued sample streams at  $6 + 6b^1$  resolution [10] and resulting in a total of 16 GHz per sideband per polarization of science quality data. However, only one of these options could be selected for the detailed design analysis within the specified time limit. After preliminary assessment of the two first-F sub-banding options, we found that Option 1 is a significantly better match (requiring fewer FPGA multiplier resources and logic), and hence a much lower risk option for achieving the 4x BW goal for the AVCC stage (see Section 11). Thus, Option 1, assuming that the back-end of the Digitizer subsystem produces 10 x 1.6 GHz sub-bands of science quality data per sideband per polarization, was employed for the detailed design study reported here.

<sup>&</sup>lt;sup>1</sup> Containing 6-bit real-component and 6-bit imaginary component

In the first phase of this study, the design and functional verification of a single instance of a two-stage<sup>2</sup> Oversampled Polyphase Filter-Bank (OSPFB) for segmenting sub-bands into FSs was conducted using Intel's DSP design tool 'DSP Builder' in the model-based design environment MATLAB/SIMULINK, followed by compilation and timing analysis to ensure the design a) functionally performs as expected, and b) performs those functions at the required speed. In the second phase, 20 instances of OSPFBs and the other required firmware blocks to deliver 20 sub-bands to the OSPFBs and FS switching fabric to select and route the resulting 80 FSs x 2 pols to ALMA Frequency Slice Processors (AFSPs), were instantiated. The result of the compilation of this design is that ~65% of the primary logic resources are utilized and F<sub>max</sub> of 470 MHz is achieved, where 450 MHz is the minimum requirement.

Given this FPGA resource use, the fact that the logic instantiated and compiled is close to the final design—and in fact is the final OSPFB design—and that F<sub>max</sub> of 470 MHz was achieved, we are at least 95% confident that the final AVCC FPGA design will fit and operate in the required FPGA at 450 MHz.

<sup>&</sup>lt;sup>2</sup> This is not, functionally, another "F" stage of the AT.CBF FFX design—it is an optimization the "first-F".

## 2 Background

In the 2018 ALMA Development Roadmap [3], at least doubling the correlated bandwidth of ALMA has been identified as its number one near-term priority. This was based on the vast array of science opportunities that would be facilitated by this upgrade, especially in the key science areas of the *Origins of Galaxies, the Origins of Chemical Complexity, and the Origins of Planets*. In aggregate, this upgrade (including upgrades to the upstream digital system and upgraded receivers) has come to be known as the *"ALMA2030 Wideband Sensitivity Upgrade"* with a goal for completion before the end of this decade (though some receiver bands may be upgraded later).

In response, the Front-End/Digitizer Working Group [4] recommended that the goal should be 4x the current correlated bandwidth because both front-end receiver and digitizer technology were sufficiently mature to make that feasible, in particular that 16 GHz per sideband per polarization should be digitized and transmitted to the correlator. Subsequently, the Correlator Specifications Working Group [5] recommended that at minimum the 2<sup>nd</sup> Generation ALMA Correlator should be able to produce at least 2x the current bandwidth initially (8 GHz per sideband per polarization) and have a plan to expand it to 4x correlated bandwidth.

In 2020, the correlator design team from Herzberg Astronomy and Astrophysics, National Research Council Canada (HAA-NRC) participated in the ALMA Development Study - Cycle 7 and submitted a report [6] on how to adapt their Correlator and Beamformer (CBF) based on the TALON Frequency Slice Architecture (TALON FSA) for the 2<sup>nd</sup> Generation ALMA Correlator. The TALON FSA CBF is based on FFX architecture and has been proposed for the SKA Mid.CBF and advanced through multiple review stages including the final design review and is currently being prototyped. Based on this study, in April 2021, HAA-NRC in collaboration with NRAO<sup>3</sup>, submitted a proposal to design and build the 2<sup>nd</sup> Generation ALMA Correlator [7]. After a successful outcome in the NA down-selection and approved by the NSF, this proposal was selected to move forward for a full review and consideration by the ALMA Project and Board. The proposed design, called the ALMA TALON Central Signal Processor (AT.CSP) is comprised of three main elements: the ALMA TALON Correlator Beam Former (AT.CBF), the ALMA TALON Correlator Data Processor (AT.CDP), and the ALMA TALON Hardware in the Loop Simulator (AT.HILS). The AT.CBF has two stages: first, the ALMA Very Coarse Channelizers (AVCCs) where the digitized sequences are segmented into oversampled 'Frequency-Slices' (FSs) containing 200 MHz of usable bandwidth, followed by ALMA Frequency Slice Processors (AFSPs) where the FSs are Resampled into the sample rate of 221.184 Ms/s and corrected for delay/phase and then further segmented into 13.5 kHz wide fine channels and cross-correlated between up to 70 antennas. The original proposal had the limitation that while it could AVCC-channelize and AFSP-correlate 2x bandwidth (16 GHz per pol) and was expandable, it lacked the ability to flexibly select what part of the total 32 GHz per pol expected to be produced by the digitizers (i.e., 16 GHz per pol per sideband), could be correlated.

Subsequent to the NA correlator project down-select, in July 2021, the Digitizer Team at the Laboratoire d'astrophysique de Bordeaux (LAB), University of Bordeaux, France published their final Study report [8] confirming that digitization of 16 GHz per sideband per polarization at a sample rate of 40 GS/s would be feasible. Additionally, the LAB study report indicated the preference to perform a coarse channelization (e.g., 2 GHz of usable bandwidth per sub-band) using oversampled polyphase filter-banks (OSPFBs) to be

<sup>&</sup>lt;sup>3</sup> for the correlator software development.

instantiated in FPGAs that are needed to interface to the ADCs and facilitate serial data transmission over an optical network. In other words, to perform a "first-F" at the antennas, though preserving the time-series nature of the digitized signal.

Shortly after release of the Digitizer Study Report, cross-subsystem discussions between the LAB and NRC-NRAO teams and a few ESO and NRAO representatives were held in August to October 2021. A number of options for achieving the desired science flexibility between the 4x bandwidth digitizers and 2x bandwidth (initially) AT.CSP were explored. At the same time, the AT.CSP design was evolving to use the innovative "Async-Talon" approach recently developed for the SKA-mid correlator design [9]<sup>4</sup>. This approach significantly reduces the resources required in the AVCCs of the AT.CBF because, DDR4 memory in the AVCCs is no longer required for bulk delay compensation, such delay effectively now occurring in the AFSPs' corner-turner where large memory is required anyway. Furthermore, a twostage implementation (see section 4.1.2) of an oversampling channelizer can further reduce the number of multipliers needed for AVCC implementation. The combination of these two design improvements opened the highly desirable possibility that, within the current capped-budget allocation (which has been capped by the NA Development Program), each AVCC (each with 2 FPGAs) could in fact handle the full 40 Gs/s digitized output (32 GHz of science bandwidth) per polarization from the digitizers compared to just 16 GHz per polarization in the original design. In this scenario, no first-F at the antennas is required, from the AT.CSP point of view, for the purpose of limiting the data transmitted to an (initial) correlation capacity of only 2x BW.

Since the ALMA Management Team had already confirmed that it would be highly desirable to make the path towards eventual expansion to 4x BW correlation a priority, this 3-month NA Development Study was initiated to confirm that with the new design improvements, the AVCC stage could process the raw 40 Gs/s digitized data stream (16 GHz of bandwidth per sideband per polarization) prior to submission of the full proposal to the ALMA Board. If successful, eventual AT.CSP bandwidth expansion would only require additional AFSP hardware. It should be emphasized that the detailed design work for the AVCC stage presented in this study report would have been required in the early stages of the AT.CSP project (if approved) anyway, i.e., it represents a significant jump-start toward completion of the final detailed AT.CSP design.

In the meantime, lack of consent on the need for a first-F at the antennas led to a 'mini-review' by the ALMA Integrated Development Team (IDT) on 13th of October 2021<sup>5</sup>. Alternatives were presented by both teams, and unsurprisingly, the compromise design presented by both teams, was chosen. In the agreed design, the 32 GHz of science bandwidth per polarization in the 40 Gs/s sequence will be segmented into sub-bands within the Back-end subsystem. These sub-bands are then transferred to the AT.CBF and further segmented into FSs in the AVCCs. One key topic was not resolved at the mini-review, namely the exact nature of the first-F sub-banding, though the NRC and LAB teams agreed to consider two options:

Option 1: Sampled at 2.0 Gs/s containing 1.6 GHz (3.2 GHz for DSB) of bandwidth and

<sup>&</sup>lt;sup>4</sup> The "Async-Talon" [9] approach was developed for the SKA-mid correlator, was subjected to a stringent external review (in process during the original AT.CSP proposal preparation and submission), and was approved. <sup>5</sup> After the proposal for this study [1] was submitted, but before its start.

Option 2: Sampled at 2.5 Gs/s containing 2.0 GHz (4.0 GHz for DSB) of bandwidth,

both consisting of complex-valued sample streams at 6 + 6b<sup>6</sup> resolution [10] and a total of 16 GHz per sideband per polarization of science quality data. As a result of these decisions, the aforementioned scope of the study was revised to address the first-F at the antenna baseline plan, though with the understanding that only one of the two sub-banding options could be carried through to the detailed AVCC design stage, after a preliminary evaluation. As described in Section 11, this evaluation indicates that Option 1 provides a significantly better match to the AT.CSP architecture with lower multiplier and logic requirements. Therefore, the following study report only considers the detailed design and implementation of over-sampling channelizers to segment sub-bands sampled at 2.0 Gs/s containing 1.6 GHz (3.2 GHz for DSB) of bandwidth, into 200 MHz FSs. That is, we assume that the raw 40 Gs/s digitized data stream will be sub-banded at the antennas into 10 x 2.0 Gs/s per sideband per pol sub-bands, each sub-band containing 1.6 GHz science quality bandwidth for a total of 16 GHz per sideband per pol.

<sup>&</sup>lt;sup>6</sup> Containing 6-bit real-component and 6-bit imaginary component

## 3 Study Approach

The purpose of this 3 month long study is to determine the feasibility of handling a total of 32 GHz bandwidth (16 GHz x 2 polarizations) contained in 20 sub-bands with one ALMA Very Coarse Channelizer (AVCC) Stratix-10 1SX280HU2F50E1VG FPGA. The main signal processing firmware blocks in an AVCC FPGA are the 10-channel OSPFBs that segments the 1.6 GHz bandwidth contained in a sub-band at the sample rate 2.0 Gs/s into 8 FSs containing 200 MHz of bandwidth. Hence, it requires 20 OSPFBs to process the total bandwidth of 32 GHz. Further, there are firmware blocks to deconstruct and reconstruct data frames to facilitate data transmission to and from the AVCC. Confirming that all required firmware blocks can be instantiated in the selected FPGA device and configured such that the signal processing functions are performed at the desired rate facilitating the expected data throughput will retire significant risk for the full 2<sup>nd</sup> Generation Correlator Project Proposal that is to be submitted to the ALMA Board in April 2022.

The step-by-step description of the study is given in the following;

- Carried out the design and functional verification of the OSPFB using Intel 'DSP Builder' [11] blocks within the model-based design environment provided by Simulink/MATLAB [12]. The OSPFB design was modularized such that key signal processing operations such as the polyphase FIR filter-banks, parallel 10-point IFFT and the array of Half-Band filters (see Section 4.1.2) were separated into different modules along with input and output data arrangement and scaling and re-quantizing.

- Configured the auto-generation of the HDL code for the OSPFB targeting Intel's Stratix-10 1SX280HU2F50E1VG FPGA. The auto-generated code was verified with RTL simulations using 'ModelSim' with the test-vectors generated by DSP Builder and MATLAB [13]. This is to verify that the generated HDL code for the OSPFB performs the DSP and logic functions as expected.

- 3. Carried out multiple compilation flows for a single instance of OSPFB in the selected FPGA with the Intel's Quartus Prime Pro design suite [14] and reviewed the key FPGA resource utilization metrics and the Static Timing Analysis (STA) leading to F<sub>max</sub> estimates. After each run, modifications were made to the DSP Builder design such that F<sub>max</sub> exceeded the operational clock-rate at 450 MHz with a margin of 150 MHz. This margin was considered to be sufficient to increase the possibility of timing-closure when 20 instances of the OSPFB and other required firmware blocks are added to the design.

- 4. Modified the HDL code and encapsulated with a HDL 'wrapper' such that it is compatible with the existing framework that have been developed for the firmware development and verification for the Talon Demonstrator Correlator (TDC). This in turn allowed the straight-forward use of key firmware blocks (e.g. 100G Ethernet MAC, Sync-FIFO (single-clock synchronous FIFO) and Circuit Switch firmware blocks) that have already developed.

- 5. Incrementally integrated up to 20 instances of OSPFB firmware designs and conducted compilation flows. The utilization of primary resources, routing congestion and F<sub>max</sub> estimates were scrutinized.

6. Incrementally integrated up to six<sup>7</sup> 100G Ethernet MACs, up to six Sync-FIFO firmware blocks to mimic the wideband Input Buffers (WIBs) in the Async-Talon design and two actual 80x80 12-bit wide Circuit Switch firmware blocks that cross-connect the FSs from OSPFB firmware blocks to serial output channels, which ultimately are connected to AFSPs.

<sup>&</sup>lt;sup>7</sup> All four of configurable high-speed transceivers in the Stratix-10 SX2800 FPGA and two soft-core transceivers. The final implementation will likely only include five 100G transceivers, since 6+6b data fits on this many 100G links (480 Gbps of data), and distributing data received on five links to 20 OSPFBs is much simpler than six.

## 4 Overview

### 4.1 The Basics of Oversampled Polyphase Filter-Banks

#### 4.1.1 Single Stage Implementation of Oversampled Polyphase Filter-Banks

The main objective of an oversampled polyphase Filter-Bank is to segment the input bandwidth without gaps and to have no significant spectral leakage in the central part of the channel that is to be further segmented into finer bandwidths. This is achieved at the expense of slightly higher sampling rate for each segmented output. Given that a complex-valued input  $x_i(n_i)$  at the rate of B samples per second is corresponding to a critically-sampled sequence of a 'flat' input spectrum  $X(e^{j\omega})$ , with respect to normalized angular-frequency  $\omega/\pi$ , is shown in Figure 4-1-(a). The objective is to segment this bandwidth equally to be carried by  $N_{ch}$  channels.

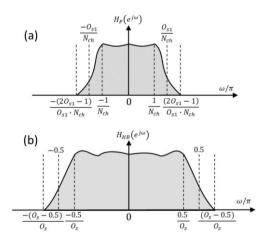

Consider a typical magnitude response of the Finite Impulse Response (FIR) low-pass 'prototype' filter  $H_P(e^{j\omega})$  is shown in Figure 4-1-(b). In general,  $H_P(e^{j\omega})$  is symmetric and therefore the filter coefficients  $h_P(n)$  are *real-valued*. Note that for  $\omega/\pi > 0$ , nominally the passband and stopband edges of  $H_P(e^{j\omega})$  are at  $\omega_p/\pi = 1/N_{ch}$  and  $\omega_s/\pi = (2O_s - 1)/N_{ch}$  respectively [15](Ch.09). Here,  $O_s > 1$  is the over-sampling factor. In practice  $\omega_p$  is selected to be slightly higher than  $\pi/N_{ch}$  such the magnitude responses of channels of the subsequent channelizer that are at the vicinity of  $\omega_p$  would not be degraded. Similarly,  $\omega_s$  would be decreased by the same amount in order to avoid excessive aliasing. Also, it is straightforward to have a linear phase response for  $H_P(e^{j\omega})$  by selecting an even-order of filter [15](Ch.03).

A direct although not efficient way of evaluating the output sequence for  $k^{\text{th}}$  channel ch[k](n), is to first modulate the filter-coefficients  $h_P(n)$ , by  $e^{j\frac{2k\pi}{N_{ch}}n}$ , such that the magnitude response  $H_P(e^{j\omega})$  is shifted right by  $\omega/\pi = 2k/N_{ch}$  and fall between  $((2k-1)/N_{ch}, (2k+1)/N_{ch})$ .

The output of the filter is evaluated by convolving the input sequence  $x_i(n_i)$  with the modulated filter coefficients and then down-sampled by an integer factor of L, where:

$$L = \frac{N_{ch}}{O_s}.$$

(4-1)

Therefore, the sample rate for each output channel ch[k](n) is  $B/L \equiv (B \cdot O_s)/N_{ch}$ . Note that due to placing the passband of the modulated filter coefficients within the Nyquist region, the resulting spectrum after down-sampling may not always center at  $\omega/\pi = 0$  [16](Ch.04). Hence, a post down-sampling modulator is required to re-orient the spectrum around  $\omega/\pi = 0$ . An example of the resulting magnitude spectrum  $Ch[k](e^{j\omega})$  for ch[k](n) is shown in Figure 4-1-(c). It can be shown that the spectral components of  $Ch[k](e^{j\omega})$  within the range  $(-1/O_s, 1/O_s)$  correspond to the spectral components of the input spectrum  $X(e^{j\omega})$  within the range  $((2k - 1)/N_{ch}, (2k + 1)/N_{ch})$ , which is identified by 'Chk' in Figure 4-1-(a) scaled with the 'passband-ripple' of  $|H_P(e^{j\omega})|$ , within the range  $(-1/N_{ch}, 1/N_{ch})$ . There can be some spectral leakage due to the finite attenuation of  $H_P(e^{j\omega})$  in the stopband (i.e. beyond  $\omega_s/\pi$ ) and aliasing back due to the down-sampling operation. Note that, in theory,  $H_P(e^{j\omega})$  can be designed to have an arbitrarily small passband ripple and an arbitrarily higher

stopband attenuation at the expense of a filter having higher number of coefficients that leads to a higher implementation complexity, a longer temporal response, and increased power consumption.

A more efficient architecture for realizing the above signal-processing operations is shown in Figure 4-2 [15](Ch.09). Note that the prototype-filter  $H_P(z)$  has  $N_h$  coefficients. As shown in Figure 4-2, the input sequence  $x_i(n)$  is fed into a tapped delay line (TDL) -buffer of length  $N_h$  in blocks of *L*-samples. That is, the  $n^{\text{th}}$ -block contains the samples  $x_i((n-1)L+1)$  to  $x_i(nL)$  in the natural order with the most recent sample at the left. For each such block, a frame of outputs  $\{y[k](n)\}; k = 0, 1, ..., N_{ch} - 1$  is evaluated such that:

$$y[k](n) = \sum_{l=0}^{[(N_h - 1)/N_{ch}]} TDL(k + N_{ch} \cdot l) \cdot h_P(k + N_{ch} \cdot l),$$

(4-2)

where  $(k + N_{ch} \cdot n)$  refers to the set of elements containing the  $k^{\text{th}}$  element and every  $N_{ch}^{\text{th}}$  element until the final element of the sample vector.

Next, the parallel  $N_{ch}$  outputs are 'rotated by  $(N_c - L)$  for each frame of outputs from the polyphase FIR filters. This operation re-orients the extracted bandwidth around the center of the channel<sup>8</sup>. After the Input Rotation,  $N_{ch}$ -point Inverse Fast Fourier transform (IFFT) of  $\{y[k](n)\}$  is evaluated such that:

$$ch[k](n) = \sum_{m=0}^{N_{ch}-1} y[m](n) \cdot e^{j\frac{2\pi mk}{N_{ch}}}; \text{ for } k = 0, 1, 2, \dots, N_{ch} - 1.$$

(4-3)

<sup>8</sup> If this input-rotation is not performed, a parallel complex-modulation with  $\left\{e^{j\frac{2\pi Lk}{N_{ch}}n}\right\}$ , for  $k = (0, 1, ..., N_c - 1)$ , then has to be performed on the outputs of the IFFT to re-orient the channelized spectrum [15](Ch.09).

Figure 4-2 Single stage OSPFB architecture.

#### 4.1.2 Two Stage Implementation of Oversampled Polyphase Filter-Banks

In [15](Ch.13), it has been shown that a cascading implementation of a OSPFB and an array of low-pass filters can achieve the required performance with significant computational savings. This is due to the fact that a prototype filter for the OSPFB with a wider transition-band requires fewer coefficients compared to a one with a narrower transition-band [15](Ch.13).

Consider the example shown in Figure 4-3, where the oversampling factor  $O_{s1}$  of the OSPFB has been selected to be twice the desired oversampling factor  $O_s$  (i.e.  $O_{s1} = 2O_s$ ). This in turn increases the transition-band of the prototype filter for the OSPFB by up to 50% and thereby, in general reduce the required number of coefficients by up to a factor of 4 [16](Sec.3.2.4). However, this would produce channels at twice the sample rate than the desired. Hence, before down-sampling by factor of two to achieve the desired sample rate these channels have to be filtered by a low-pass filter to avoid aliasing. As proposed in [15](Ch.13), 'Half-Band' filter would be an efficient way of performing this filtering. For Half-Band filters, almost half of the coefficients are zeros and the rest of coefficients are symmetric and therefore, only a half of the multipliers are needed to implement a Half-Band filter compared to a general low-pass filter with symmetric coefficients. The typical magnitude responses of the prototype filter of the OSPFB for stage-1 and the Half-Band filter for the two-stage implementation of the OSPFB is shown in Figure 4-4.

Array of Half-Band Filters

Figure 4-3 System view of a two stage OSPFB.

Figure 4-4 Typical magnitude responses of the prototype filter of the OSPFB for stage-1 (a) and the Half-Band filter (b) for the above two-stage implementation of the functionality of OSPFB.

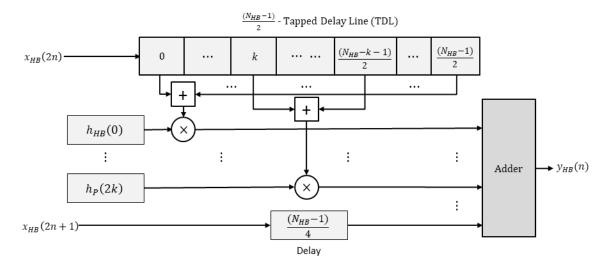

For the two stage implementation of an OSPFB, an efficient implementation of a Half-Band filter that minimizes the required number of multipliers is shown in Figure 4-5. In this example the order of the Half-Band filter is  $(N_{HB} - 1)$ , which must be an even integer but not a multiple of 4. Note that due to the down-sampling by factor of two, only the input samples with even-indices are fed into the 'tapped delay line' (TDL) shown in top of Figure 4-5. On the other hand the input samples with odd-indices are fed into a delay of  $(N_{HB} + 1)/4$  samples. The value of 'single' filter coefficients that convolve with samples with odd-indices is 0.5 and with binary 2's complement arithmetic's can be impended trivially with shifting the bits of input sample to the left by one position and therefore, does not need a dedicated multiplier. Further, coefficients that convolves with samples with even-indices are symmetric and therefore the corresponding two samples can be added before being multiplied as shown in Figure 4-5. Hence, just  $(N_{HB} + 1)/4$  dedicated multipliers are needed to implement this Half-Band filter. However, this comes with restriction in the control of stopband attenuation and passband ripple. Overall, the effective impulse response of the two stage OSPFB is *slightly*<sup>9</sup> longer than that of a single stage OSPFB.

<sup>&</sup>lt;sup>9</sup>This is an inconsequential effect for ALMA since having a short enough impulse response for timing pulsars using VLBI beam data is required, and such is dominated by further downstream processing in the AFSPs.

Figure 4-5 An efficient implementation of a Half-Band filter.

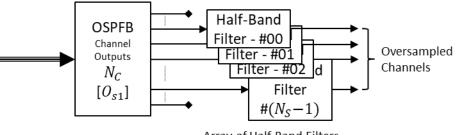

## 4.2 The Proposed Architecture of the Two-Stage Oversampled Polyphase Filter-Bank for Sub-Band Processing

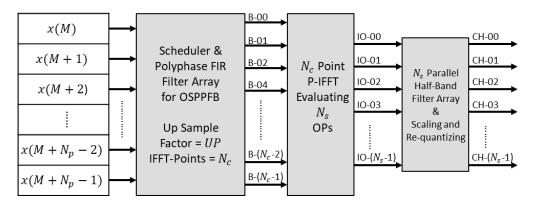

The two-stage OSPFB architecture [15](Ch.13) that has been proposed for extracting FSs from the subbands in AVCC FPGAs is shown in Figure 4-6. The main objective is to reduce the number of total multipliers needed such that 20 OSPFBs running at 450 MHz clock rate can be instantiated in a single Stratix-10 1SX280HU2F50E1VG FPGA to process a total of 32 GHz of bandwidth. The input to each OSPFB is complex-valued samples arranged in frames containing  $N_p = 5$  contiguous complex-valued samples and producing  $N_s = 8$  complex-valued FSs. Note that for the input sample frames both the real and imaginary components are conveyed to the OSPFB simultaneously whereas the output FSs the real and imaginary components are time interleaved in one stream.

Figure 4-6 Proposed architecture of the OSPFB for extracting FSs from the sub-bands.

The key parameters associated with the selected option are listed in Table 4-1. Note that in order to support the two stage design for the OSPFB with the given input sample rates while achieving the specified output bandwidth, the input samples are nominally up-sampled by a factor of two with insertions zero valued samples. This effectively duplicates the spectrum within the principal Nyquist

range [15](Ch.2) and therefore more than one-half of the output channels can be dropped. This further reduces the computations required to perform in the Parallel-Inverse Fast Fourier Transform (P-IFFT).

| Input<br>Sample<br>Rate<br>(Gs/s) | Obs<br>BW<br>(GHz) | Number of<br>samples in<br>an Input<br>Frame (N <sub>p</sub> ) | second | Real /<br>Complex<br>Valued<br>Data | Up<br>Sampling<br>Factor | Over<br>Sampling<br>Factor | IFFT<br>Points | Selected<br>FSs per<br>OSPBF<br>(N <sub>s</sub> ) | FS Sample<br>Rate<br>(Ms/s) |

|-----------------------------------|--------------------|----------------------------------------------------------------|--------|-------------------------------------|--------------------------|----------------------------|----------------|---------------------------------------------------|-----------------------------|

| 2.0                               | 1.6                | 5                                                              | 400E6  | Complex                             | 2                        | 10/9 ≡<br>1.111            | 10             | 8                                                 | 222.22                      |

Table 4-1 The key parameters associated with the OSPFBs.

The scheduler (see Figure 4-6) arranges the input samples to be processed by polyphase FIR filters. The flow of input data is controlled by a First-In-First-Out (FIFO) buffer in the scheduler. Due to zero insertion up-sampling, one-half of the samples are zero and therefore, only one-half of the coefficients are required to be multiplied with the corresponding samples. Depending on the state, an array of 2:1 Multiplexers are used to direct the input samples and the corresponding coefficients to the specific 'multiplier adder blocks' (see Figure 4-2). The outputs of these multiplier adder blocks are then subjected to input rotation. If the number of IFFT-points are even, then an array of 2:1 Multiplexers are used to direct the rotated samples to one of two sub-IFFT blocks further reducing the number of resources.

The selected outputs  $N_s = 10$ , of the P-IFFT block yields a sample rate twice the required rate and the selected outputs are further processed by an array of  $N_s$  identical Half-Band filters where the downsample by a factor of two operation has already incorporated into their architecture (see Figure 4-5). The outputs of these Half-Band filters are arranged such that the real and imaginary components are time multiplexed. The data paths from the input to and outputs of the Half-Band filters are gradually expanded such that to avoid signal saturation. Hence, in order to maintain the desired signal level and reduce the size of the 80x80 FS circuit switch in the FPGA, and data transmission rate to the AFSPs, the outputs of these Half-Band filters are scaled and re-quantized to 8+8b resolution, introducing an inconsequential sensitivity loss.

## 4.3 An Example Design of the Two-Stage Oversampled Polyphase Filter-Bank for Sub-Band Processing

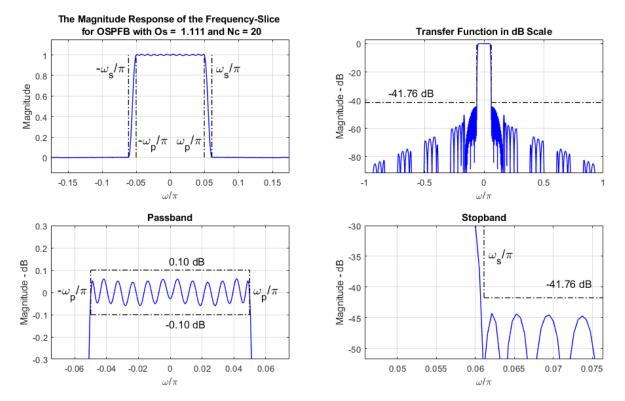

Following the specifications for passband and stopband edges given in the Section 4.1.2, the prototype filter for the stage-1 OSPFB and the corresponding Half-Band filters are designed to achieve combined stopband attenuation of 41.76 dB<sup>10</sup> and that maintains combined passband ripple within  $\pm 0.1$  dB using built in functions in MATLAB.

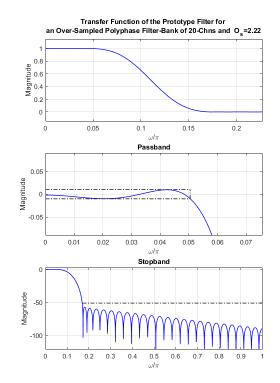

The prototype filter for the stage-1 OSPFB that meets required specifications is of order 54 and its magnitude response is shown in Figure 4-7. The top pane shows the magnitude response in linear scale illustrating the extended transition-band. As shown in the middle pane the passband ripple is constrained within  $\pm 0.01$  dB and in the bottom pane the stopband attenuation is several dBs better

<sup>&</sup>lt;sup>10</sup> i.e. 1:15,000 instantaneous dynamic range.

than the minimum required 41.76 dB threshold. Note that the passband ripple and stopband attenuation can be constrained with better control for the prototype filter of the stage-1 OSPFB compared to the Half-Band filter.

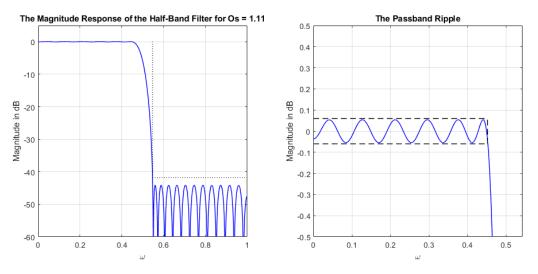

To meet the required specifications, the order of the Half-Band filter should be higher than 46. The magnitude response of the Half-Band filter of order 46 is shown in Figure 4-8. The stopband attenuation, shown in the left pane of Figure 4-8, is only a couple of dBs better than the required 41.76 dB threshold and the passband ripple, shown in the right pane of Figure 4-8, is within  $\pm 0.06$  dB.

Figure 4-7 Magnitude response of the prototype filter for the stage-1 OSPFB.

Figure 4-8 Magnitude response of the Half-Band filter of order 46.

The combined magnitude response of the prototype filter of the stage-1 OSPFB and the Half-Band filter is shown in Figure 4-9. The four panes confirm that the requirements are met.

Figure 4-9 Combined magnitude response of the prototype filter of the stage-1 OSPFB and the Half-Band filter.

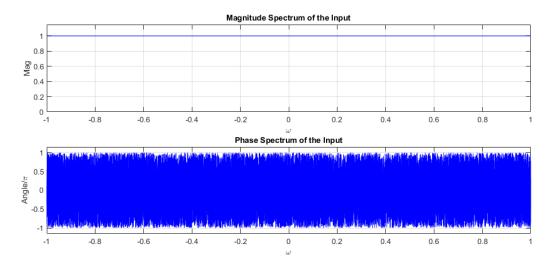

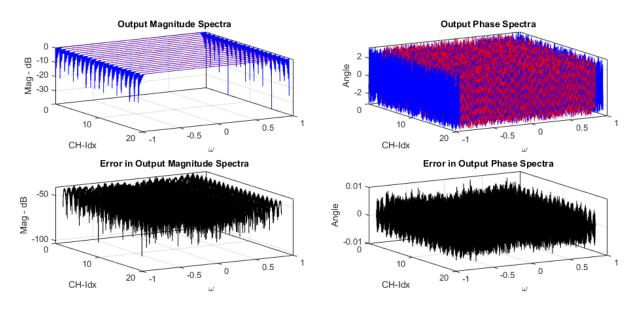

The initial functional verification of the two-stage OSPFB has been achieved through simulations with test vectors synthesized with collections of sinusoids with known magnitude and phase. FFT methods have been exploited to efficiently evaluate these test vectors. In the following example, the input spectra is selected to consist of uniformly spaced sinusoids with unit magnitude and uniformly distributed phase as shown in Figure 4-10. The corresponding magnitude and phase spectral and the segmented inputs and the corresponding output channels after gain correction compensating for the passband ripples due to combined responses of the stage-1 OSPFB and the Half-Band filter are shown in Figure 4-11 (top). The differences in magnitude and phase between the gain corrected outputs and segmented inputs are shown in Figure 4-11 (bottom).

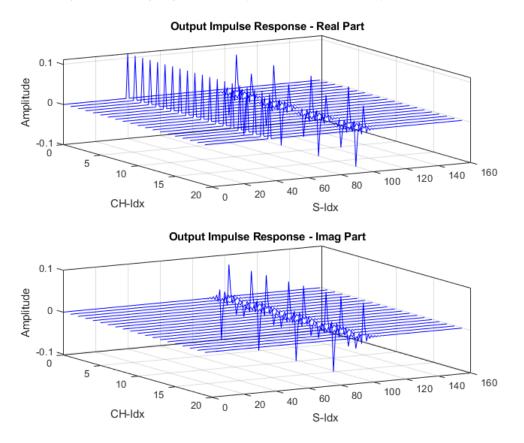

The impulse response of the OSPFB has been studied using impulsive inputs with unit magnitude placed at different time-slots of the commutator frame. The real and imaginary -components of the responses for each FS for a selected impulsive input are shown in (top) and (bottom) of Figure 4-12. It has been observed that these outputs span maximum of 27 samples (i.e. 121.5 ns). Hence, a flagged input sample<sup>11</sup> would affect 27 output samples at maximum. This fact has been used in the firmware design in

<sup>&</sup>lt;sup>11</sup> Such is normally only for RFI flagging purposes. The AT.CSP proposal is compliant to requirement 6.2.11 of [5] no RFI flagging on the real-time data stream is planned, although such could be done if necessary. In the FPGA design done for this study, the mechanism for carrying RFI flags is included, but the logic to generate flags is not.

flag-extension logic. Further, this also shows that the OSPFB has an algorithmic propagation delay of 13 samples. Note that the actual latency through the FPGA implementation of the OSPFB is higher.

Figure 4-10 Magnitude (top) and phase (bottom) spectra of the input test vector to the OSPFB.

Figure 4-11 Top-Row : Magnitude (left) in dB-scale and phase (right) spectra of the output channels (blue) after gain correction and the corresponding segmented spectra of the input test vector (red) to the OSPFB. Bottom-row: Differences between segmented input and output magnitude (left) in dB-scale and phase (right) spectra.

Figure 4-12 Impulse responses of the OSPFB: real-part (top) and imaginary-part (bottom). The impulse response spans a maximum of 27 output samples.

## 5 Key Study Work Elements

- Design an OSPFB using Intel's DSP Builder to process a sub-band at the sample rate 2.0 Gs/s and yield 8 FSs containing 200 MHz of observation bandwidth targeting Intel Stratix-10 1SX280HU2F50E1VG FPGA.

- 2. Generate the HDL code for the OSPFB that is ready for implementation with the selected Intel Stratix-10 1SX280HU2F50E1VG FPGA.

- 3. Verify the functionality of the HDL implementation of the OSPFB using ModelSim with the stimuli generated using MATLAB/SIMULINK.

- 4. Configure an AVCC FPGA design that contains 20 instances of OSPBFs, six 100G Ethernet MACs to receive the sub-band data from the Digitizer subsystem, six Sync-FIFO buffers (mimicking WIBs), two 80×80 Circuit Switches to direct the 160 FSs (i.e. 80 FS x 2 polarizations) generated by the 20 OSPFBs to different AFSPs for downstream processing and Device Tree Interface (DeTrI) interconnect linking up the configurable registers associated with aforementioned firmware blocks.

- 5. Make incremental changes to the firmware blocks, in particular the OSPFB design such that 20 instances can operate at the FPGA clock rate of 450 MHz<sup>12</sup>.

- 6. Compile the entire design, analyze timing, and make design changes/iterate until timing closure is achieved for the required processing clock rates, which is normally 450 MHz, but may be higher or lower in some cases.

<sup>&</sup>lt;sup>12</sup>This operational clock rate is required to process a total of 32 GHz bandwidth containing in sub-bands resulting a total of 160 FSs each containing 200 MHz.

## 6 Design Details

### 6.1 Interfaces

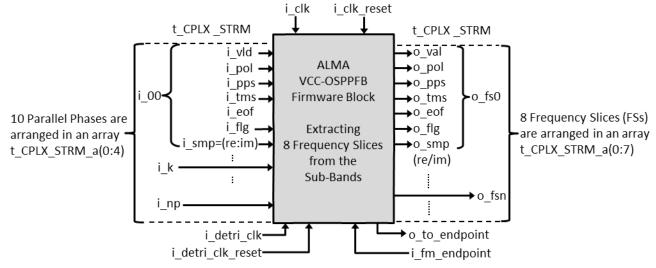

The interface to the ALMA OSPFB firmware block is illustrated in Figure 6-1. The input and output signals to and from the firmware block are arranged into a record array (i.e. 't\_CPLX\_STRM\_a') of the VHDL record 't\_CPLX\_STRM' that delivers the real and imaginary components of the associated sample and other control signals. The components of the record 't\_CPLX\_STRM' are listed in Table 6-1.

Figure 6-1 Input/output interfaces for the ALMA OSPFB segmenting the sub-bands and generating FSs.

| Record<br>Component | Description                                                                                                                                                                                                                                                                            |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _val                | The valid marker that indicates the associated sample is valid or not.                                                                                                                                                                                                                 |

| _pol                | In the input, this signal doesn't represent any significance. In the output, this marks the real (=0) or imaginary (=1) component of the time-interleaved _smp output                                                                                                                  |

| _pps                | The 'Time-Epoch' marker. In the input this marks 0.048 s time period and in the output marks 0.144 s period.                                                                                                                                                                           |

| _tms                | The 64-bit 'Time-Code' that is aligned with the '_pps' marker.                                                                                                                                                                                                                         |

| _eof                | The 'End of Frame' marker that indicate the end of frame for serial 'framed' data.<br>(Not used in the input of the OSPFB)                                                                                                                                                             |

| _flg                | The 'Flag' is asserted to mark either saturated or contaminated samples and several other scenarios given in the following.                                                                                                                                                            |

| _smp.re<br>_smp.im  | The real/imaginary components of the sample expressed in 'sfixed' format containing<br>up to 18 -bits. The binary point is right of the most significant bit and therefore, the<br>signal amplitude is in the range [-1,+1]. Note that in the output only the real part is<br>non zero |

| Table 6-1 | Components of the VHDL record 't_ | CPLX STRM'. |

|-----------|-----------------------------------|-------------|

|           |                                   |             |

From the remaining signals, 'i\_clk' and 'i\_clk\_reset' signals drive the firmware block and resets the datapath, respectively. The 'i\_detri\_clk' signal drives the set of registers that can be either written or read by a processor that has access to the FPGA fabric. The 'i\_detri\_clk\_reset' resets the content in these registers. The 'i\_fm\_endpoint' and 'o\_to\_endpoint' signals collectively represent the handshake signals, address-bus and data-bus for the 'control' interface with the processor facilitated by the custom 'DeTrl' interface [17].

In the input, five consecutive complex-valued samples of a sub-band sample stream are packed into to an array of records 't\_CPLX\_STRM\_a(0:4)' that consisted of 5 't\_CPLX\_STRM' records where the real and imaginary parts of each of the five associated samples are assigned to i\_smp.re and i\_smp.im, respectively. This is illustrated in Figure 6-2. Note that the oldest sample in the sample array is in the top associated with the 0<sup>th</sup> record 't\_CPLX\_STRM\_a(0)'. Also, the samples corresponding to the 48 ms markers from the digitizer are expected always to be in the 0<sup>th</sup> record 't\_CPLX\_STRM\_a(0)' with i\_pps='1'. Note that the input complex-valued samples are in the format (6+6b) and therefore, the 12 least significant bits of i\_smp.re and i\_smp.im are set to zero (i.e. i\_smp.re/im(-6:-17) = '0').

| t_CPLX_STRM_a(0) | i_smp.re = re[x(5·(n+1))]<br>i_smp.im = im[x(5·(n+1))]                       | <br>i_smp.re = re[x(5·(n+m))]<br>i_smp.im = im[x(5·(n+m))]                   |

|------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| t_CPLX_STRM_a(1) | $i\_smp.re = re[x(5 \cdot (n+1)+1)]$<br>$i\_smp.im = im[x(5 \cdot (n+1)+1)]$ | <br>$i\_smp.re = re[x(5\cdot(n+m)+1)]$<br>$i\_smp.im = re[x(5\cdot(n+m)+1)]$ |

| t_CPLX_STRM_a(2) | $i\_smp.re = re[x(5 \cdot (n+1)+2)]$<br>$i\_smp.im = im[x(5 \cdot (n+1)+2)]$ | <br>i_smp.re = re[x(5·(n+m)+2)]<br>i_smp.im = re[x(5·(n+m)+2)]               |

| t_CPLX_STRM_a(3) | i_smp.re = re[x(5·(n+1)+3)]<br>i_smp.im = im[x(5·(n+1)+3)]                   | <br>i_smp.re = re[x(5·(n+m)+3)]<br>i_smp.im = re[x(5·(n+m)+3)]               |

| t_CPLX_STRM_a(4) | $i\_smp.re = re[x(5 \cdot (n+1)+4)]$<br>$i\_smp.im = im[x(5 \cdot (n+1)+4)]$ | <br>i_smp.re = re[x(5·(n+m)+4)]<br>i_smp.im = re[x(5·(n+m)+4)]               |

| Figure 6-2 | Arrangement of the real and complex components of the input samples of the sub- |

|------------|---------------------------------------------------------------------------------|

|            | band in the record array 't_CPLX_STRM_a(0:4)'.                                  |

In the output, the eight FSs are arranged into an array of records 't\_CPLX\_STRM\_a(0:7)'. Note that o\_pps marks the sample corresponding to every third i\_pps corresponding to an interval of 144 ms<sup>13</sup>. Also, the 64-bit time-code o\_tms is only valid when o\_pps is asserted. In between o\_pps marks, o\_tms to remain unchanged. Further, o\_eof, signal is asserted to indicate the last valid sample before the subsequent o\_te marker. The output samples are of format (8+8b) and as opposed to inputs the real and imaginary components are time interleaved and marked accordingly with o\_pol = '0' for real component and o\_pol = '1' for imaginary component, respectively. Hence, o\_smp.re(-8:-17) = '0' and o\_smp.im(0:-17) = '0'.

<sup>&</sup>lt;sup>13</sup>In an FS, at the sampling rate of 222.222. Ms/s there are 10,666,666.6667.. samples in every 48 msec. In order to mark o\_tms exactly at the corresponding sample, the marking interval has been increased to 144 msec such that there are exactly 32,000,000 samples between the two o\_te marks.

### 6.2 Monitor and Control

The registers for monitor and control of the ALMA OSPFB firmware block along with some description are listed in Table 6-2. Each register is 32-bits wide and can be accessed in 8-bit (byte-wide) segments.

| Offset<br>Address | Read /<br>Write                                                                 | Register<br>Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | Some<br>are<br>read –<br>only<br>(RO)<br>some<br>are<br>read –<br>write<br>(WR) | Flag Status      | <ul> <li>Bit 00 (RO): i_pps marker has not arrived. Auto reset to '0' when the first i_pps arrives.</li> <li>Bit 01 (RO): The expected number of valid samples has not received between two consecutive i_pps markers. Auto reset to '0' when the expected number of valid samples are received between two i_pps markers.</li> <li>Bit 02 (RO): The FIFO in the data scheduler has been overflown. Fatal condition! Need reset to resolve this.</li> <li>Bit 03 – 04 (RW): Selection of eight consecutive channels from the ten possible outputs of the OSPFB.</li> <li>00 – Selects Ch#1 : Ch#8 as Fs-00 : FS-07</li> <li>01 – Selects Ch#2 : Ch#9 as Fs-00 : FS-07</li> <li>10 – Selects Ch#0 : Ch#7 as Fs-00 : FS-07</li> <li>Bit 05 – 31 : Reserved</li> </ul> |

| 1                 | R/W                                                                             | Sft_Scl_00       | The shift* (bits 19-16) and scale† (bits 15-0) of the gain factor for FS-00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2                 | R/W                                                                             | Sft_Scl_01       | The shift (bits 19-16) and scale (bits 15-0) of the gain factor for FS-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3                 | R/W                                                                             | Sft_Scl_02       | The shift (bits 19-16) and scale (bits 15-0) of the gain factor for FS-02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4                 | R/W                                                                             | Sft_Scl_03       | The shift (bits 19-16) and scale (bits 15-0) of the gain factor for FS-03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5                 | R/W                                                                             | Sft_Scl_04       | The shift (bits 19-16) and scale (bits 15-0) of the gain factor for FS-04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6                 | R/W                                                                             | Sft_Scl_05       | The shift (bits 19-16) and scale (bits 15-0) of the gain factor for FS-05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7                 | R/W                                                                             | Sft_Scl_06       | The shift (bits 19-16) and scale (bits 15-0) of the gain factor for FS-06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8                 | R/W                                                                             | Sft_Scl_07       | The shift (bits 19-16) and scale (bits 15-0) of the gain factor for FS-07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 6-2 List of monitor and control registers for the ALMA OSPFB firmware block.

\* 'Shift', a 4-bit unsinged integer derives the shift of the binary point of the samples of the particular FS to the left.

+ 'Scale', a 16-bit unsinged normalized fractional number, scales the samples of the particular FS, before being quantized to 8-bits. Note that for addresses 1 - 8, bits 20 - 31 are reserved.

#### **Criteria for Assertion of Flags**

- 1. o\_flg is asserted for valid outputs until the first i\_pps marker arrives. The 00-bit of the read register at the offset address 0 is also asserted to match with this.

- 2. o\_flg is asserted for until the data pipelines of the OSPFB are filled (i.e. for 27 valid output samples) with valid inputs since the first i\_pps marker.

- 3. If i\_flg is asserted in an input frame, o\_flg is asserted for the subsequent 27 valid output samples indicating contaminated outputs.

- 4. If the firmware block doesn't receive the expected number of valid samples between two consecutive i\_pps markers after the initial i\_pps has arrived, o\_flg is asserted until the expected number of samples are received between consecutive i\_pps markers. The 01-bit of the read register at the offset address 0 is also asserted/deasserted to match with this.

- 5. If the FIFO in the scheduler (see Figure 4-3) has overflown o\_flg is asserted until the firmware block is reset. The 02-bit of the read register at the offset address 0 is also asserted to match with this.

- 6. o\_flg is asserted for individual samples, if the outputs saturate when re-quantize to (8+8b)words after shifting/scaling.

### 6.3 Internal Architecture