One Gigabit per Second - 128-Track Option

VLBA One Gigabit per Second Tape Drive Upgrade

Technical Feasibility Study

Version 12

VLBA Data Acquisition

Memorandum #399

Produced by: NRAO AOC Data Acquisition Group

George Peck, Steven Durand

April 3, 2000

National Radio Astronomy Observatory

National Radio Astronomy Observatory

P.O. Box O, 1003 Lopezville Road, Socorro, New Mexico 87801-0387

Telephone: (505) 835-7000 Fax: (505) 835-7027

Introduction *

Options for Implementation *

Data Acquisition Rack Hardware Considerations *

Formatter Upgrades *

MVME117 Module *

Timing and Control *

Digital Switch *

Header Control *

Transport Driver *

Quality Analysis Module *

Fringe Check Data Buffer Module *

Card-cage, Back-plane, and Rack *

Power Supply *

Output Rate Synthesizer *

32 MHz Synthesizer *

Sampler *

5 MHz Distributor *

IF Distributor *

Baseband Converter *

DAR Estimated Cost *

DAR Schedule *

Recorder Hardware Considerations *

General Requirements *

Head Assembly Upgrades *

Inchworm Motor *

Head-block Housing *

Headstacks *

Pre-amp Boards *

Read / Write Interface Boards *

Upgrade Requirements by Module *

Head Assembly *

Read Interface Module *

Write Driver Module *

MVME117 Module *

VME Transport Module *

VME Monitor Module *

VME Write Module *

Inchworm Controller Module *

Analog Conditioner Module *

XVME540 AD/DA Module *

Cables *

Power Supplies *

Recorder Firmware Considerations *

Recorder Estimated Cost *

Recorder Schedule *

Head Performance *

Head 2 Error Rates *

Head 1 Error Rates *

Head 1 Error Rates with Head 2 Movement *

Write Performance *

Tape Format *

Correlator Considerations *

Playback Drive Upgrade *

Parallel Reproduce Module *

VME Clock Recovery Module *

Playback Head Assembly *

Read Interface Module *

Playback Estimated Cost *

Playback Schedule *

Conclusion *

Appendix A. VLBA Recorder and Formatter Budget *

Appendix B. Playback Tape Drive Budget *

This paper discusses expanding the present VLBA Data Recording System from a peak aggregate data rate of 512 Megabits per second, (8 Mbps per track), to an aggregate data rate of 1024 Megabits per second (1-Gbps). The method described is referred to as the 128-track Option in publication "The VLBA Gigabit-per-second Data Recording System", J.D. Romney, New Astronomy Reviews, 43,523 (1999). This option adds a second headstack to each of the two recorders and a second VLBA formatter at each site. Proposed sites included the 10 VLBA recording stations, the VLA and the Green Bank Telescope.

The upgrade provides the capability to record a total of 128 tracks simultaneously at a bit-rate of 8 Mbps, for an aggregate data rate of 1-Gbps. This method takes advantage of existing designs and hardware and does not require the tape speed to exceed 160 inches per second. The required changes to the VLBA station-control software can be accommodated within the framework already in place to support the 64-track recording mode.

The upgrade uses two VLBA recorders operating in parallel. Each recorder will have a double head assembly capable of recording 64 tracks simultaneously. It is proposed that there be three forward passes and three reverse passes, for a total of six passes. Twelve VLBA headstack locations are to be utilized on the tape (2 locations per pass). The typical operating time between tape changes for the 1-Gbps upgrade is 2 hours and 15 minutes. Manpower requirements at the VLBA sites are greatly increased for the 1-Gbps upgrade, since the time between tape changes is very short and tapes must be changed on both drives at each tape change.

There are two competing methods to support 1-Gbps data recording: a128-Track, 8-Mbps per Track Option and a 64-Track 16-Mbps per Track Option.

128-Track, 8-Mbps per Track Option

This approach adds a complete VLBA formatter and a second headstack to each of the recorders. Two recorders are used in parallel to record 128 tracks simultaneously at a maximum bit rate of 8 Mbps per track and 160 ips. This option is close to the original VLBA DRS design concept. The necessary changes to the VLBA station-control software could be accommodated within the framework already in place that uses both drives simultaneously to support 64-track recording.

64-Track 16-Mbps per Track Option

This approach also uses two recorders in parallel but instead of using two headstacks per recorder, a single headstack is used at twice the data rate (16 �Mbps) and the tape moves at 320 ips.

Tests have been carried out at 16-Mbps and a cross talk problem has been identified. At 16-Mbps, the Mark IV drives operate close to the resonant frequency of the present heads. There is excessive coupling between the heads at the resonant frequency thus causing cross talk. A lower inductance and a higher resonant frequency headstack is being developed to address this problem. Presently, recording at 16-Mbps is marginal, but work is still being done to improve performance.

The following formatter options could be implemented for the 1-Gbps upgrade:

- Add a VLBA formatter to each site.

- Install two Mark IV formatters at each site, and retain the VLBA formatter.

- Add a Mark IV formatter at each site, and use the existing VLBA formatter and the Mark IV formatter simultaneously.

Most of the features of the VLBA formatter are also included in the design of the Mark IV formatter. There are, however, two major differences. One major difference is that the Mark IV formatter is able to output data bits at a maximum rate of 16 Mbps, for 320 ips recording. The VLBA formatter can output data bits at a maximum rate of 8 Mbps, for 160 ips recording. The other difference is the Mark IV format is a "data replacement" format, and the VLBA format is a "non data replacement" format. The Mark IV format discards 0.8% of the data when frame headers are inserted in the data stream. The VLBA format does not discard data bits when frame headers are inserted.

Some minor differences between the formats also exist. The VLBA format writes the Modified Julian Date, and counts seconds all day long in the time-code field. The Mark IV format writes the last digit of the year, the day number, hours, minutes, and seconds. The Mark IV format calculates the Cyclic Redundantly Check (CRC) over the all data bits of the frame header. The VLBA format calculates the CRC over the data bits of the time-code field. The VLBA formatter writes the recorder number and the Data Acquisition Rack (DAR) number (which could be used for the formatter number) in the frame header. The Mark IV formatter does not write this information in the header, but it does write eight status and error bits. The VLBA format reserves the last 8 bits of the header as spares, and the Mark IV formatter has 2 spare bits within the 8 bits of error and status information. These minor differences have little impact on the scientific results.

The Mark IV formatter does not include a QA module, however a Mark IV QA module has been designed that is outside of the formatter. If a Mark IV formatter is used for the 1-Gbps upgrade, either the Mark IV QA module or the VLBA formatter could be used to obtain QA results, phase cal extraction, and data buffering. The Mark IV QA module has the same error rate capabilities as the VLBA formatter QA module. It can extract phase cal tones from 4 channels of data, while the VLBA formatter can extract phase cal tones from up to 16 channels of data. It includes a 480 Mbit data buffer, compared to a 4 Mbit data buffer in the VLBA formatter. This data buffer can capture data off of the tape as well as in real time, while the VLBA formatter data buffer can only capture data in real time. The data can be transferred out of the module in a matter of seconds, whereas it takes more than 20 minutes to transfer the data out of the VLBA formatter data buffer. In spite of the advantages of the Mark IV QA module, the capabilities of the VLBA formatter are sufficient in the areas of QA, phase cal extraction, and data buffering for operation and maintenance.

Presently, the cost of a single Mark IV formatter is estimated to be $39K. The Mark IV QA module has never been built commercially, but is estimated to cost about $10K.

As of March 2000, certain aspects of the Mark IV formatter firmware are not yet complete. Track ID and Channel ID have not been implemented. The QA phase cal capability of the QA module is not yet developed.

If the Mark IV formatter and/or QA module is used for the 1-Gbps upgrade, some design work would be necessary to interface the Mark IV equipment to the VLBA stations. An interface would have to be developed between the VLBA monitor and control bus and the Mark IV formatter. VLBA software would have to be developed that would control the Mark IV equipment. A patch cable would be necessary between the Mark IV formatter and the VLBA tape drives. The VLBA sampler modules would require some minor modification as well.

The 128-Track, 8-Mbps per Track Option has been selected as the best option to support 1-Gbps recording. This option uses existing hardware and methods. Recording at 160 ips on thin tape has been proven reliable. In addition the present recorders have provisions for additional headstacks and the support electronics.

Option 1 in the Formatter section, adding an additional VLBA formatter to each site, is also recommended. This is the least expensive option. It would require less effort because new designs and interfaces would not be required. The VLBA formatter design is complete, robust, and reliable and the present advantages of using the VLBA format could be retained.

The following sections describe in detail the tasks required to implement the 128-Track, 8-Mbps per Track Option using the VLBA formatter.

Data Acquisition Rack Hardware Considerations

Each of the following will have to be added to each site, a VLBA Formatter, a VME Card-cage, a Back-plane, and two power supplies. An additional 19 " rack will be required house the additional equipment.

The Formatter design consists of seven boards based on VME bus architecture. 1) The MVME117 Module, 2) Timing and Control (T/C), 3) Digital Switch, 4) Header Control (H/C), 5) Transport Driver (T/D), 6) Quality Analysis (Q/A), and 7) Fringe Check Data Buffer (D/B). The cards are interconnected via three VME back planes. The interface circuitry to the VME bus is identical for each module except for the VME addresses. Rotary switches that are mounted on each board establish the address for each module.

Seventeen sets of hardware will be assembled, ten for the VLBA sites, one for the VLA, one for the Green Bank Telescope, one for the VLBA test station at the AOC, one for the Laboratory and three spare sets. The costs for parts and labor for each module are presented in the last section.

The MVME117 Module is a single board VME (CPU) computer that is used as the controller for the Formatter. The firmware, maintained by NRAO, is stored on a pair of EPROMs.

One MVME117 Module is required for each site 1-Gbps upgrade.

The Timing and Control module distributes the transport clock, generates system control based on values retrieved from the format definition array, processes interrupts, interfaces to the MCB, maintains the time-code, generates control signals for data track (barrel) rolling, monitors system status and supplies �12vdc to the MVME117 module. The Timing Control Module receives control information for the Output Rate Synthesizer module via the VME Bus from the MVME117 Module. A cable is connected from the P3 Back-plane to the Output Rate Synthesizer Module with 4 control lines. These lines control the output frequency of the Output Rate Synthesizer Module. The Output Rate Synthesizer Module controls the rate at which data is clocked out of the Formatter.

One Timing and Control Module is required for each site 1-Gbps upgrade.

The Digital Switch module is responsible for track switching, track multiplexing/de-multiplexing, track output mapping, Phase Cal extraction, and state counting. The function of the Phase Cal extraction circuit is to detect signals at selected frequencies between 10 kHz and 16 MHz. In the 1-bit mode, 16 Phase Cal extractors are available. In the 2-bit mode, 8 Phase Cal extractors are available. Any of the incoming channels from the Sampler Modules can be inputs to the Phase Cal extractors.

Two Digital Switch Modules are required for each site 1-Gbps upgrade.

The Header Control module contains the FIFO memory, the auxiliary data RAM, the track roller logic. The module generates the four system tracks and inserts the serial time-code, test data and control bits into the data bit-stream.

Two Header Control Modules are required for each Site 1-Gbps upgrade.

The Transport Driver module contains circuitry for generating and inserting parity, track id, CRC, and bit modulation. Data enter the Transport Driver Module from the Header Control module via the P3 backplane. The data are converted from binary to NRZM. Data going in to the output drivers for each individual track can be enabled and disabled. The output drivers send each track to the VME WRITE Module of the tape drive on a differential pair. One, two, or four tracks are sent to the Fringe Check Data Buffer Module via the VME backplane. Identical data are sent to drive #1 and drive #2.

Two Transport Driver Modules are required for each Site 1-Gbps upgrade.

The Quality Analysis module receives 2 channels of data and clocks from each tape drive via the P3 backplane. The main function of the module is to check for parity errors, CRC errors, resync errors, and no-sync errors. There is also a circuit that extracts phase cal tones from the 2 channels of data, which is used routinely for system testing. An additional QA module is needed for the 1-Gbps upgrade, because the time required for readback tests would be doubled if only one QA module is used.

One Quality Analysis Module is required for each Site 1-Gbps upgrade.

Fringe Check Data Buffer Module

This module contains the 4 Mbit memory that is used to capture data from up to 4 tracks. When a capture command is received from the user, data are captured beginning at the next one-second epoch. The data can be transferred to the station computer via the MCB, and can be used for a "real time" fringe check with other stations. The station computer is capable of doing an auto-correlation and FFT on the data, and displaying a spectral plot on the screen.

One Fringe Check Data Buffer Module is required for each Site 1-Gbps upgrade.

Card-cage, Back-plane, and Rack

The card cage accepts twelve 9U-VME Modules, with a small section on the left side for three 6U-VME modules. The Formatter utilizes only one 6U module (the MVME117 CPU board). There are 3 backplanes, P1, P2, and P3. P1 is the highest backplane, and it extends across the entire card cage. Every VME module plugs in to the P1 backplane. The P2 backplane is split in to two parts. One part is for the 6U module on the left, as well as the leftmost 9U module (the QA module). The other part of the P2 backplane is for the remaining 9U modules. The P3 backplane is a custom backplane, and also extends across the entire card cage. The formatter is part of the Data Acquisition Rack.

An additional three feet tall 19" rack is required at each site.

The two power supplies located near the top of the Data Acquisition Rack power the Formatter. The P105 power supply provides +5 volts, and the P107 power supply provides -5.2 volts. The power supplies are shared with other modules in the rack. The P107 supply is a Lambda LRS-54-5, and is capable of outputting 40 amps at 25 degrees C. The P107 supply in the lab at the AOC draws 22 amps. The P105 is a Lambda LRS-56-5, and is capable of outputting 90 amps at 25 degrees C.

Two Power Supplies are required for each Site 1-Gbps upgrade.

The Output Rate Synthesizer provides the clock that is used to clock data out of the Formatter. The frequency of this clock is set by control signals from the Formatter. The clock is locked to the 5 MHz signal from the maser.

The output rate clock provided by the Output Rate Synthesizer is needed for the second Formatter in the 1-Gbps upgrade. If the existing Output Rate Synthesizer Module provides the clock at the VLBA stations, it must be determined if the existing module can drive 2 formatters. There is only one output for the output rate clock on the module. If the same Output Rate Synthesizer Module is used to drive both formatters, then both formatters will be constrained to output data at the same rate.

No additional Output Rate Synthesizer modules are required for the 1-Gbps upgrade.

The 32 MHz Synthesizer Module provides the 32 MHz clock to sample the data and the buffered 1 Pulse-Per-Second (PPS) to the Baseband Converter and IF Distributor Modules. It also provides a "sync" pulse to the Formatter. The inputs to the 32 MHz Synthesizer Module are the 5 MHz timing signal and the 1PPS from the Station Timing Module. The 32 MHz clock is synchronized to the first positive going transition of the 5 MHz signal following the 1PPS. On the second positive going transition of the 5 MHz timing signal, following the 1PPS, the "sync" pulse, which is 31.25 ns wide, is generated. This "sync" pulse is sampled by the sampler module, and sent to the Formatter. It is used by the Formatter to identify the first data sample in each 1-second epoch.

The second Formatter will receive the 32 MHz clock and the "sync" signal through the sampler cables from the Data Acquisition Rack which is already present at all VLBA sites.

No additional 32 MHz Synthesizer Modules are required for the 1-Gbps upgrade.

Two Sampler Modules sample the analog data from the Baseband Converter Modules, (BBCs). Two bit (4 level) sampling is performed on each channel. Each Sampler Module also samples the 32 MHz clock and the "sync" pulse from the 32 MHz Synthesizer Module. Signals from BBCs 1-4 are sampled by Sampler Module #1, and signals from BBCs 5-8 are sampled by Sampler Module #2. The sampled data are sent to the Formatter through 1 ribbon cable from each Sampler Module. Each bit-stream is a differential ECL pair.

Each driver chip (MC10131) in the Sampler Modules presently drives two MC10125 receiver chips in the 512 Mbit/sec Formatter. For the 1-Gbps upgrade, each MC10131 driver chip must drive four MC10125 receiver chips. The ribbon cables from the Sampler Modules to the second Formatter must be longer than the present ribbon cables.

No additional Sampler Modules are required for the 1-Gbps upgrade.

The 5 MHz Distributor Module accepts the 5 MHz frequency standard and distributes it to the Baseband Converters, IF Distributors, Output Rate Synthesizer, and the 32 MHz Distributor. This frequency standard originates from the Maser.

No additional 5 MHz Distributor Modules are required for the 1-Gbps upgrade.

Two IF Distributor modules accept the four intermediate frequencies in the range of 480 MHz to 1020 MHz. The IF Distributor Modules accept the intermediate frequencies from the vertex room of the VLBA antenna, or alternatively from the external input BNCs on the front panels of the IF Distributor modules. IF Distributor module #1 accepts intermediate frequencies A and B. IF Distributor module #2 accepts intermediate frequencies C and D. There is a power detector with a selectable integration period for each IF Distributor Module. A 20 dB attenuator can be switched in to the signal path for any of the IF signals by the user. Each Intermediate Frequency is sent to all 8 of the Baseband Converters.

No additional IF Distributor Modules are required for the 1-Gbps upgrade.

Each of eight Baseband Converter modules accepts the four Intermediate Frequencies from the IF Distributor modules. The main function of Baseband Converter is to convert the Intermediate Frequency down to Video or Baseband frequency. One of the four Intermediate Frequencies is selected as the input to each Baseband Converter. There is a local oscillator in the module that is tunable between 500 MHz and 1000 MHz. It is locked to the 5 MHz signal that originates from the Maser. The output of the local oscillator is mixed with the selected IF to produce the Baseband signal. Each Baseband Converter produces two outputs, a lower sideband and an upper sideband, that are each sampled by the samplers. There is a low-pass filter on each lower and upper sideband output. The user sets the bandwidth of the filter. There are 9 possible settings, in multiples of 62.5 kHz, up to a maximum of 16 MHz. There is gain control circuitry to amplify the signal, and a power detector, with selectable integration period, to measure the amplitude of the output signal.

No additional Baseband Converter Modules are required for the 1-Gbps upgrade.

Seventeen sets of hardware will be assembled; ten for the VLBA, one for the VLA, one for the Green Bank Telescope, one for the VLBA test station at the AOC, one for the Laboratory and three spare sets. The total cost for upgrading the Data Acquisition Rack is about $826,000, (loaded $1,530,000). The cost breakdown by module is shown in appendix A.

The manpower estimate for the upgrade project is 9,400 man-hours of about 55% technician and 45% engineer. This equates to about 4.7 man-years.

Recorder Hardware Considerations

The original recorder was designed to support two head assemblies with dual headstacks in each. Thus space is presently available for the additional circuitry that is needed. Some of the necessary additional circuits are already in place, and are presently used as spares. The present recorder 19" Rack can accommodate the 1-Gbps upgrade both physically and electrically. Figure 1 shows the rear view of the recorder with the new modules referred to as #2. Only two new modules will be required, a Read Module #2, and a Write Module #2.

Figure 1. Expanded Recorder Rack Rear View

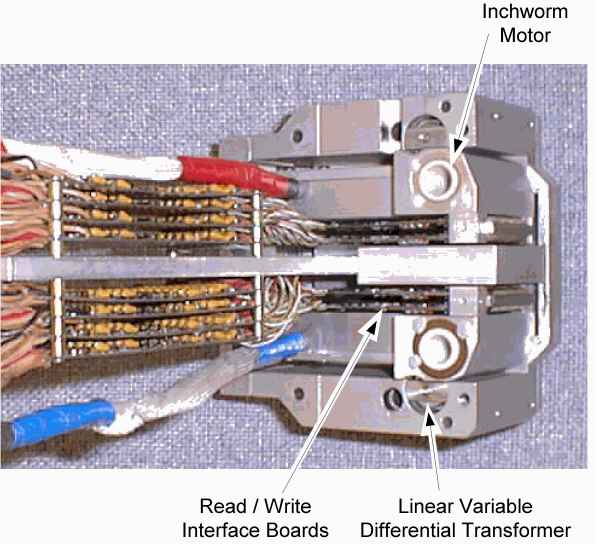

The main components of the present head assembly include a fixed dual block mount, two head block housings, one set of pre-amp and interface boards, a septum stiffener, and one set of interface cables. The following components attach to the first head block housings: headstack, inchworm motor, and LVDT position sensor. Presently, a dummy headstack attaches to the second head block housing.

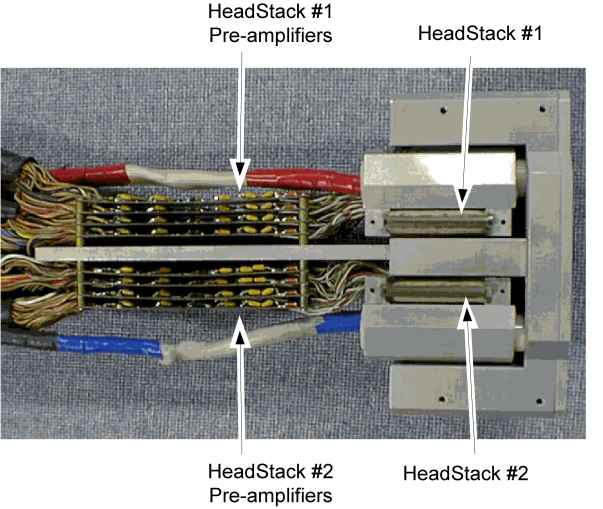

All of the existing head assemblies must be modified for the 1-Gbps upgrade. The dummy headstack must be removed from the second head block housing, and the following components must be added: headstack, inchworm motor, and LVDT position sensor. The following components must also be added to the head assembly: two interface boards, four pre-amp boards, and a cable set. A completed dual assembly is shown in figure 2. Each of the components will be described individually in the following sections.

Figure 2. Head Assembly with Both Headstacks and Preamplifiers

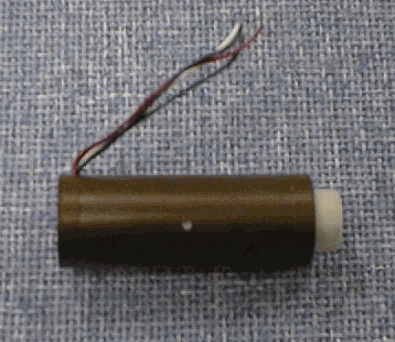

Burleigh manufactures the Inchworm Motor, figure 3. The motor consists of three piezoelectric elements along a linear shaft. Each element is an electro-mechanical device that undergoes a dimensional change when a voltage is applied. The conversion of electrical energy into mechanical motion takes place without generating a significant magnetic field. The outer two elements act as clamps and the central element expands and contracts along the shaft as the voltage is applied. Each step of the inchworm motor is about 4 nanometers.

Figure 3. The Inchworm Motor

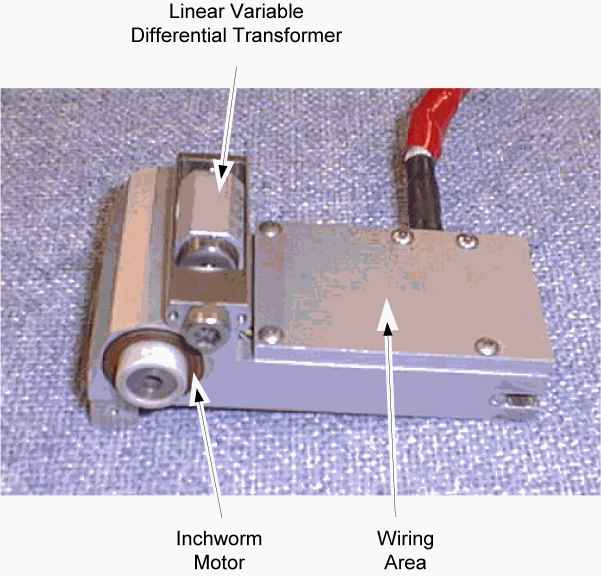

The Head-block Housing, figure 4, holds a Headstack, an Inchworm Motor, and a Linear Variable Differential Transformer (LVDT). The LVDT is used to measure the absolute position of the headstack. The upgrade will require that an additional Head-block Housing be installed in each Head Assembly.

Figure 4. The Head-block Housing

High track densities are achieved by utilizing headstacks of 36 heads separated with a pitch of 698.5 microns. Each headstack is mounted on a separate Head-block Housing. Two Head-block Housings, figure 5, are required for the upgrade.

Presently four pre-amp boards are required for each head assembly. Each pre-amp board contains the circuitry for 9 heads. Four additional pre-amp boards are required for the upgrade.

Two Read/Write Interface Boards are required for each headstack. The interface boards contain a back-to-back diode and an emitter follower for each head. Two additional Read/Write Interface Boards are required for the upgrade.

Figure 5. The completed Headstack assembly including the Upgrade

Upgrade Requirements by Module

The present head assembly consists of a fixed dual block mount, 2 head block housings, one set of pre-amp assemblies and one set of interface cables. The head block housing holds a headstack, an Inchworm motor and a LVDT position sensor. The upgrade includes adding the following parts to the existing head assemblies: Headstack, Inchworm Motor, LVDT, two Interface Boards, four Pre-Amp boards, and a cable set. Twenty-nine head assemblies will be modified for the 1-Gbps upgrade; two for each of the 10 VLBA sites, two for the VLA site, two for the Green Bank telescope, two for the AOC laboratory and three spares.

The Read Interface module receives all 36 tracks from the head assembly. Two of these tracks are selected for quality analysis and power detection. These two selected tracks are sent to the VME Monitor Module for clock recovery and decoding. Channels A and B each have a BNC connector on the front panel of the module located on the back of the recorder. Channel A connects to the total power detector cable, and both BNC connectors can be utilized as test points. There are 6 selection bits each associated with channels A and B for track selection. There are also 2 selection bits each associated with channels A and B for equalizer select. All selection bits originate in the VME Monitor Module. After passing through the track selection logic, the circuitry amplifies and equalizes the signal. A comparator changes the signal to TTL levels and provides a differential signal to the VME Monitor Module.

One additional Read Interface module is required for each 1-Gbps upgrade.

The Write Driver Module contains the final amplification for the write circuit. All 36 tracks enter the module through 2 connectors (even and odd) from the VME Write Module. A variable write voltage from the analog power supply is applied to DS0026 chips that control final amplification. This amplified write signal is sent to the head assembly through two connectors on the rear panel. Just after the write amplifiers, the signals are tapped for the "bypass mode" circuitry. These select bits come from the VME Monitor Module. The two selected tracks are provided the VME Monitor Module for quality analysis and decoding.

One additional Write Driver Module is required for each 1-Gbps upgrade.

The MVME117 Module is a single board VME computer that is used to control the tape drive. The firmware is maintained by NRAO, and resides on a pair of EPROMs on the module. This module is similar to the MVME117 module used in the Formatter.

No additional MVME117 modules are required for the 1-Gbps upgrade.

The VME Transport Module contains circuitry that controls motion of the tape and headstack. Other functions include the MCB interface and generation of interrupts to the MVME117 Module. The headstack motion control signals enter the module from the VME backplane, and are sent to the Inchworm Controller, as discussed in the Inchworm Controller Module section. Tape motion logic includes the capstan reference generator; the reel pack detectors, the footage counter, low tape logic, and vacuum sense logic. Firmware from the MVME117 Module uses the VME Transport Module to energize the reel servo system and control the reel motor brakes.

No additional VME Transport Modules are required for the 1-Gbps upgrade.

The VME Monitor Module receives the 2 tracks selected for quality analysis from the Read Interface Module or the Write Drive Module. A clock recovery chip recovers a clock synchronous with the data in each channel. For channels A and B, the data and the recovered clocks are sent to the QA module of the Formatter for quality analysis. Selection bits for track and equalizer selection are received via the VME bus from the CPU board. These select bits are then sent to the Read Interface and Write Driver Modules through a ribbon cable. Channel A or Channel B is sent to the mini-decoder where 32 consecutive bits are decoded and available to the user via the MCB.

The VME Monitor module does not require modification for the 1-Gbps upgrade. It was designed and built to receive data and recover clocks from 2 headstacks. The only required activity is check-out and QA.

The VME Write Module is sent data from 72 formatter tracks (both sets of boards from the 512 Megabit formatter). There are 72 outputs, 36 to headstack 1 and 36 to headstack 2. Any head group from the formatter can be channeled to the corresponding head group of either headstack of the tape drive. A head group consists of low odds, low evens, high odds, or high evens. Each head group is enabled or disabled at the output of the module. If a head group is disabled in the VME Write Module, that head group will not record the tape. After all head groups have been assigned, system track selection takes place. Any track of headstack #1 or headstack #2 can be assigned to any one of the system tracks (0, 1, 34, or 35) of the same headstack.

No additional VME Write Modules are required for the 1-Gbps upgrade. The VME Write Module does not require modification for the 1-Gbps upgrade. The only required activity is checkout and QA

The Inchworm Controller Module controls the high voltage piezoelectric Inchworm Motor. The circuit board is printed with circuits for 4 Inchworm Motors. The circuit board is stuffed with parts to control two Inchworm Motors. The Inchworm Controller Module receives the following inputs from the VME Transport Module: device select (dev 1, dev 2, dev 3, and dev 4), reverse (or "in"), forward (or "out"), stop, fast, and slow. There are 4 connectors (9 pin) which are outputs to the 4 Inchworm Motors. Each Inchworm motor receives the following signals from the Inchworm Controller: inner clamp (black, pin 4), axial expander (green, pin 3), outer clamp (red, pin 5) and compensation voltage (white, pin 9). The Inchworm Controller Module requires 110-volts for a transformer to provide the high voltage (740 volts). There is a logic board that receives inputs from the VME Transport Module. The logic board contains circuitry that controls which clamp on the Inchworm Motor the high voltage is applied to, and whether to ramp the axial expander voltage up or down. It also contains circuitry that controls the speed of the ramp, thus determining the speed of the Inchworm Motor. There is a potentiometer on the rear panel that adjusts the clearance compensation. The clearance compensation sets the voltage for the clamps when the clamps are unclamped or off. This determines the distance between the unclamped clamps and the motor shaft. Normally, it is set at 200 volts. The Inchworm Controller Module can control only 1 Inchworm Motor at a time. The logic board receives the device select from the VME Transport Module. Even though each Inchworm Motor has its own select line, the VME Transport Module is allowed to select only one at a time.

Each Inchworm Controller Module requires the second circuit to be tested.

All monitored signals that require analog to digital conversion are amplified to the proper levels in the analog conditioner module. These signals are then sent to the VME AD/DA Module for analog to digital conversion. These signals include the LVDT, the total power detector, the vacuum pressure, and the headstack temperature. The vacuum pressure transducer is located on the rear panel of the module, and a vacuum hose plugs directly into the transducer. There are already components in place for two total power detectors, LVDTs, and headstack temperatures. The high voltage (740 volt) signals for the inchworm motor pass through the Analog Conditioner Module, but are not acted upon in any way.

The circuits for headstack 2 on the analog conditioner module have not been tested on most boards, and the connectors are not installed for headstack 2. Some extra time is required to install the necessary connectors and test the circuits for headstack 2.

The XVME-540 Module is manufactured by XYCOM, and it does all of the AD and DA conversions in the tape drive. It is capable of doing 16 AD conversions and 4 DA conversions. The AD conversions, mentioned above in the Analog Conditioner description, are carried out. DA conversions are carried out for the write voltage and the vacuum motor voltage.

No additional XVME-540 modules are required for the 1-Gbps upgrade.

Signals and power are sent to the different parts of the tape drive through cables. The only "plug-in" modules are in the VME crate. When an additional headstack is added to the tape drive, all cables in the head assembly must be duplicated. Other cables include, the VME Write Module to the Write Driver Module, the VME Monitor Module to the Write Driver and Read Interface modules, the Write Driver to the Read Interface modules, and the VME AD/DA module to the Analog Power Supply Module.

Ten additional cables are required for each 1-Gbps upgrade.

The Honeywell Unregulated Power Supply Module provides power for the tape drive. The 110-volt AC line voltage is distributed to the other power supplies in the rack, as well as to the vacuum motor and Inchworm Controller Module. This main power supply provides +/-33 volts (unregulated) for the reel servomotors and the capstan servomotor. It also provides +\-12 volts (unregulated) and +5 volts (unregulated) for the Honeywell Regulated Power Supply Module. This supply is located at the bottom of the rack. The Digital Power Supply, the Analog Power Supply, and the Honeywell Regulated Power Supply all receive power from the Honeywell Unregulated Power Supply. The Digital Power Supply provides +5 volts and �5.2 volts for the VME crate. The Analog Power Supply provides +/-12 volts, +/-15 volts, and the variable write voltage. The Honeywell Regulated Power Supply provides +/- 12 volts to the Capstan Servo Module and also to the VME Power Distribution Module.

Each Analog Power Supply Module will need to be modified to provide the variable write voltage for the second headstack. Each Honeywell Regulated Power Supply Module will also require modification to activate a time meter for the second headstack.

Recorder Firmware Considerations

The MVME117 Module is presently running a program called RECON, version 9, which was provided by Haystack Observatory. The code is written in C, and runs from a pair of EPROMs on the MVME117 Module.

For the 1-Gbps upgrade, code needs to be written to accommodate two headstacks in the drive. Three deficiencies have been found in this area. The effort to correct these deficiencies may require weeks of work.

When headstack 2 is selected as the active head, the firmware currently uses the voltage from the LVDT on headstack 1. For the 1-Gbps per second expansion project, the firmware must be changed to correct this deficiency.

MCB relative address 0x61 is the monitor point for the total power of headstack 2. It turns out that this is not yet implemented in the firmware. This is necessary for peaking, and must be done for the 1-Gbps expansion project.

MCB relative address 0x63 is the monitor point for the temperature of headstack 2. This also has not been implemented in the firmware. The VLBA has never used the temperature monitor point for headstack 1. At this time this monitor point is not needed for either headstack.

Twenty-seven sets of equipment will be assembled, twenty for the VLBA sites, two for the VLA, two for the Green Bank Telescope, one for the laboratory and two spares. The total cost for the upgrading is about $699,000 (loaded $1,310,000). The cost estimate by module for the upgrade is presented in appendix A.

The manpower estimate for the upgrade project is 5,782 man-hours of about 55% technician and 45% engineer. This equates to about 2.9 man-years.

Headstacks are the only long lead-time part required for the upgrade. Spin Physics can manufacture 3 headstacks per month. This means to obtain the required 29 headstacks lead-time is about 10 months.

A series of tests were performed using the double head assembly shown in figure 2. These tests were designed to identify what effects each of the heads had on each other. All tests were performed on January 5, 2000 using the AOC Recorder Group Formatter and the double head assembly installed in the AOC Recorder Group test drive. The head assembly was built using retired headstacks and not all heads were functioning within specification. For the test, data from only operating heads were used.

A tape from a VLBA observation was used for the test. The tape was recorded at 80 ips in VLBA1:4 format, Barrel Roll � ON, SRATE � 16M, ORATE 4.536M. The tape was played back at 160 ips.

The Parity Errors were used as the figure-of-merit indicator for each test.

Head 2 was used to read a test tape with information written on all forward and reverse tracks. The data showed good error rates on all functioning heads. Table 1 shows the complete results for tracks 22 and 24. A parity error rate of 4.0 x e-5 is better than the minimum performance VLBA specification of 3.0 x e-4.

Table 1. Head 2 Error Rates, No Movement of Either Head

|

CHAN |

SAMPLES |

PARITY |

CRC |

RESYNC |

NOSYNC |

|

22 |

7963180 |

4.0 x e-5 |

0 |

0 |

0 |

|

24 |

7958335 |

4.2 x e-5 |

1 |

0 |

0 |

Head 1 was used to read the test tape. The data showed good error rates on all functioning heads. Table 2 shows the complete results for tracks 20 and 21.

Table 2. Head 1 Error Rates, No Movement of Either Head

|

CHAN |

SAMPLES |

PARITY |

CRC |

RESYNC |

NOSYNC |

|

20 |

8182074 |

2.3 x e-5 |

0 |

0 |

0 |

|

21 |

8182075 |

4.0 x e-6 |

0 |

0 |

0 |

Head 1 Error Rates with Head 2 Movement

Head 1 was used to read the test tape while Head 2 was peaking. The data showed that movement of headstack 2 did not affect the error rates of all functioning heads in headstack 1. This test also indicates that the high volt spikes on inchworm motor 2 do not affect the error rates on headstack 1. Table 3 shows the complete results for tracks 20 and 21while headstack 2 was moving.

Table 3. Head 1 Error Rates, Head 2 Moving

|

CHAN |

SAMPLES |

PARITY |

CRC |

RESYNC |

NOSYNC |

|

20 |

8007809 |

1.6 x e-5 |

0 |

0 |

0 |

|

21 |

8007809 |

6.0 x e-6 |

0 |

0 |

0 |

The formatter was configured so that each headstack was used to write identical data. Two Write Driver modules were used but only one variable write voltage power supply was used. Since the present SCREENS menu does not support dual headstacks the write command for both headstacks were poked into the system. The power supplies were monitored to determine capacity.

The test verified that the power supplies could support the additional write current. No cross-talk problems were identified. This was anticipated since the identical headstack configuration is used at the VLBA.

The "read test with head movement" also indicates that during reading or writing either of the heads can be moved without affecting the performance of other. The inchworm controller is designed to control up to four inchworm motors one at a time. No problems are anticipated with the dual head assembly during writing.

When two recorders are used in parallel, the upgraded system is capable of recording 1-Gbps at 160 ips, (512 Mbps at 160 ips per recorder). Each headstack writes 32 tracks of data at 8 Mbps. The two headstacks in parallel are used to write three forward passes and three reverse passes per tape. Thus the operating time per tape is about 2 hours and 15 minutes and each tape holds about 4.1 Terabits.

The headstacks consist of 36 heads numbered 0 through 35. Heads 2 through 33 are used to write data while heads 0, 1, 34, 35 are used for system information. Each head is used to write in both forward and reverse. Each headstack is numbered identically but headstack 2 is installed turned 180 degrees with respect to headstack 1, figure 6. Thus track #1 of headstack 1 is written by head #1 and track #1 of headstack 2 is written by head #34.

Figure 6. Headstack and Track Locations

The tape format of head 17 in headstack 1 (HS 1) and in headstack 2 (HS 2) is shown in detail in figure 7. The three forward passes are labeled 1,3,and 5 for each headstack. The three reverse passes are labeled 2, 4, and 6. In this configuration there are 144 track groups laid down on the tape. The 1-Gbps method uses basically the same forward and reverse track locations as the VLBA recorders, Figure 8. This configuration will allow present control software to be used

Figure 7. Tape Track Physical Layout

The tracks written by each head in the forward or reverse direction are 38 microns wide and are separated by 10 microns, Figure 8. Three guard-bands are provided. The first guard-band, 23 microns, is provided between the first forward pass (Head #17 - Pass 1 forward HS 1) and the last reverse pass of the adjacent headstack (Head #16 � Pass 6 Reverse HS 2). The second guard-band, 58 microns, is provided between the last forward pass of Headstack 1 (Head #17 - Pass 5 forward HS 1) and the first forward pass of Headstack 2(Head #17 � Pass 1 Forward HS 2). The third guard-band, 23 microns, is provided between the last forward pass of Headstack 2 (Head #17 - Pass 5 forward HS 2) and the first reverse pass of Headstack 1(Head #17 � Pass 2 Reverse HS 1).

Figure 8. Heads 17 Pass Locations

The tapes recorded at the VLBA sites are played back on the 24 drives at the VLBA correlator. These drives are similar to the site drives but are configured for playback only. The following sections present one possible expansion of the playback drives.

The present VLBA Correlator has twenty station inputs, each capable of accepting aggregate data rates up to 256-Mbps, 32 data tracks operating at 8-Mbps each. Thus, a ten-station VLBA observation in the 1-Gbps mode considered in this study, could be correlated in two passes. In each pass, 32 of the 64 simultaneously recorded tracks would be reproduced from each of the twenty simultaneously recorded tapes. The two-pass correlation would take twice as long as the time spent in performing the observation.

This limit on correlator throughput is imposed by one particular subsystem of the correlator, the front-end PlayBack Interface (PBI). The PBI transmits reproduced data to the correlator proper, which operates on each input at 256-Mega samples per second. Samples are intrinsically two bits each, so that the correlator proper could operate at 512 Mbit per second if the capacity of the PBI were doubled. Such an expansion would allow the correlator to process the same ten-station 1-Gbps VLBA observation in a single pass, reproducing simultaneously all 64 tracks from each of the twenty tapes. Estimating the manpower and materials cost of upgrading the correlator PBI upgrade is beyond the scope of this study.

The present playback drives have two Parallel Reproduce Modules enabling the drive to simultaneously playback 32 tracks. There are no write modules in the playback drives. To upgrade the present drives to have a playback capability of 64 tracks would require the installation of a double head assembly, two more Parallel Reproduce Modules, a VME Clock Recovery Module, and Read Interface Module. Twenty-six sets of hardware will be assembled, 24 playback drives, and 2 sets of spares.

The Parallel Reproduce Module is used only in playback drives. Two modules are used per playback drive. Each module receives 18 tracks from the head assembly (evens or odds), and outputs 18 tracks to the VME Clock Recovery Module. The circuitry includes amplifiers, equalizers, low pass filters, and D.C. restoration.

Two additional Parallel Reproduce Modules are required for each 1-Gbps upgrade.

The VME Clock Recovery Module is also used only in the playback drives. Data from 36 tracks enter the module from the 2 Parallel Reproduce Modules. A separate clock is created for each track, which is synchronous with the data, utilizing an ATT7032 chip. The module outputs 36 data tracks with the 36 associated clocks to the playback interface of the correlator. There is a "loopback" feature where the playback interface can send a test signal with an associated clock to the VME Clock Recovery Module via the ribbon cables for the even data tracks and even clocks. When "test mode" is in use, the playback interface can send test data and clocks through the module and then it can check to see if identical data comes back from each track.

One additional VME Clock Recovery Module is required for each 1-Gbps upgrade.

Twenty-seven head assemblies will be required for the 1-Gbps upgrade: 24 correlator playback drives and three spares. The dummy headstack must be removed and the following components must be added to the second Head Block housing, a headstack, inchworm motor, and LVDT position sensor. The following components must also be added to the Head Assembly: two interface boards, four pre-amp boards, and a cable set.

Twenty-seven upgraded head assemblies are required for the 1-Gbps upgrade.

The Read Interface Module receives all 36 tracks from the head assembly. Two of these tracks are selected for quality analysis and power detection. These two selected tracks are sent to the VME Monitor Module for clock recovery and decoding. Channels A and B each have a BNC connector on the front panel of the module located on the back of the recorder. The channel A BNC connects to the total power detector cable, and both BNC connectors can be utilized as test points. There are 6 selection bits each associated with channels A and B for track selection. There are also 2 selection bits each associated with channels A and B for equalizer select. All selection bits originate in the VME Monitor Module. After passing through the track selection logic, the circuitry amplifies and equalizes the signal. A comparator changes the signal to TTL levels and provides a differential signal to the VME Monitor Module. An additional module is needed for the 1-Gbps upgrade because the correlator software must be able to make use of the mini-decoder while jobs are running.

One additional Read Interface module is required for each 1-Gbps upgrade.

Twenty 26 sets of equipment will be assembled, twenty-four playback drives, and two spares. The total cost for upgrading the Playback drives is about $729,000 (loaded $1,372,000). The cost estimate by module and for the total project is presented in appendix B.

The manpower estimate for the upgrade project is 6544 man-hours of about 55% technician and 45% engineer. This equates to about 3.3 man-years.

Headstacks again are the only long lead-time part required for the upgrade. Spin Physics can manufacture 3 headstacks per month. This means to obtain the required 27 headstacks lead-time is about 9 months.

Expanding the present VLBA Data Recording System from a peak aggregate data rate of 512-Mbps to an aggregate data rate of 1024-Mbps (1-Gbps) is feasible. No technical obstacles were discovered during this study. The total cost for upgrading the 10 VLBA sites, the VLA, the Green Bank telescope is about $1,525,000 ($2,848,000 loaded) including 5.7 man-years of labor.

The tests of the prototype dual head assembly showed good error rates on both heads during play back. Interaction tests show no affect on playback error rates of one head while the other head was moving. This allows for independent peaking of either head during playback without effecting performance. Write tests provided good results also.

The operating time for two tapes being written simultaneously, is 2 hours and 15 minutes. In a typical six-hour observation six tapes will be consumed.

It is possible to use the present playback drives and Correlator hardware to process tapes recorded in the 1-Gbps format. Each tape would have to be played back twice. Upgrading the playback drives at the AOC is also feasible. The total cost for upgrading the 24 AOC Playback drives is about $729,000 ($1,372,000 loaded) including 3.3 man-years of labor. Upgrading the Correlator playback interface is not included in this study.

The method detailed in this report increases the recorded bandwidth of the VLBA Data Recording System to an aggregate data rate of 1024-Mbps (1-Gbps) by modifying the existing drives. This method should be thought of as having a 5-10 year lifetime. A longer-term solution would replace data tape drives. NRAO is seeking an alternative recording system that is available off-the-shelf, is affordable, reliable, and expandable. A commercial drive that fulfills these requirements should be available in 5-10 years.

Appendix

A. VLBA Recorder and Formatter Budget

Connect with NRAO